Multigate device: Difference between revisions

→{{anchor|FINFET}}FinFET: add info |

|||

| Line 36: | Line 36: | ||

In September 2012, [[GlobalFoundries]] announced plans to offer a 14-nanometer process technology featuring FinFET three-dimensional transistors in 2014.<ref>{{cite web|url=http://www.eetimes.com/electronics-news/4396720/Globalfoundries-to-offer-14-nm-process-with-FinFETs-in-2014 |title=Globalfoundries looks leapfrog fab rivals with new process |publisher=EE Times |date= |accessdate=2014-03-10}}</ref> The next month, the rival company [[TSMC]], announced start early or "risk" production of 16 nm FinFETS in November 2013.<ref>{{cite web|url=http://www.eetimes.com/electronics-news/4398727/TSMC-taps-ARM-V8-in-road-to-16-nm-FinFET |title=TSMC taps ARM's V8 on road to 16 nm FinFET |publisher=EE Times |date= |accessdate=2014-03-10}}</ref> |

In September 2012, [[GlobalFoundries]] announced plans to offer a 14-nanometer process technology featuring FinFET three-dimensional transistors in 2014.<ref>{{cite web|url=http://www.eetimes.com/electronics-news/4396720/Globalfoundries-to-offer-14-nm-process-with-FinFETs-in-2014 |title=Globalfoundries looks leapfrog fab rivals with new process |publisher=EE Times |date= |accessdate=2014-03-10}}</ref> The next month, the rival company [[TSMC]], announced start early or "risk" production of 16 nm FinFETS in November 2013.<ref>{{cite web|url=http://www.eetimes.com/electronics-news/4398727/TSMC-taps-ARM-V8-in-road-to-16-nm-FinFET |title=TSMC taps ARM's V8 on road to 16 nm FinFET |publisher=EE Times |date= |accessdate=2014-03-10}}</ref> |

||

In early of 2014, http://www.digitimes.com/news/a20140328PD213.html |

|||

Pokud se na 20 nanometrů díváme z hlediska klasických desktopových procesorů a grafických karet, jde ještě o poměrně vzdálenou budoucnost (první produkty očekáváme ve druhé polovině roku - patrně spíš k jejímu konci). Ve sféře mobilních čipů jde ale o přítomnost - například Apple už má čipy A8 od Samsungu i TSMC v rukou minimálně měsíc a nyní probíhají přípravy k sériové výrobě. |

|||

I když by se mohlo zdá, že někteří výrobci (resp. designéři) přejdou rovnou na 16 nm, které jsou v těsném závěsu za 20 nm (vypadá to zatím na rozdíl tří kvartálů), bude realita spíše opačná a většina firem zůstane na 20 nm co nejdéle (k podrobnostem se ještě vrátíme). TSMC připravuje následující varianty 16nm výroby: |

|||

•16nm FinFET - Q4 2014 |

|||

•16nm FinFET+ - Q4 2014 |

|||

•16nm FinFET Turbo - 2015-2016 |

|||

O prvních dvou jsme už měli možnost slyšet. Uvedené datum značí dobu, kdy dojde ke zkušebnímu spuštění linek - v obou případech jde o konec letošního roku. Verze označená plusem by měla nabídnout zhruba o 15 % vyšší rychlost (taktovací frekvenci), přičemž tranzistorová denzita i energetické nároky nebudou negativně ovlivněny. |

|||

Plusové varianty, jejíž masová výroba je zatím plánována na samý začátek příštího roku, by měl mezi jinými využít Apple pro SoC generace A9. Třetí varianta s přídomkem Turbo je velkou neznámou. Dozvídáme se o ní poprvé a kromě označení (pravděpodobně jen pracovního), z něhož lze odhadnout cílení na nejvýkonnější segment, o ní nevíme prakticky nic. |

|||

16nm proces bude mít smysl pro ty výrobce, pro které je prioritou číslo jedna nízká spotřeba a naopak je netíží finanční stránka. Typickým představitelem takové firmy je Apple, který nemá problém nejdražší výrobní procesy zaplatit, protože produkty na nich postavené snadno a výhodně prodá. Menší firmy naopak zůstanou na 20 nanometrech co to půjde: 16nm výroba (alespoň první dvě verze) nepředstavují výrazné zmenšení čipů, hovoří se o zhruba 5 %. Cenový rozdíl přitom bude několikanásobně vyšší. Pro výrobce, jejichž prioritou je poměr cena/výkon, nebude mít minimálně 6-8 kvartálů přechod na 16 nm smysl. |

|||

Podobné to bude i na poli grafických karet a větších procesorů - produkty roku 2015 budou patrně bez výjimky 20nm a nějaké 16nm experimenty určené pro mobilní sféru uvidíme nejdříve v roce 2016, pokud vůbec. |

|||

===Tri-gate transistor=== |

===Tri-gate transistor=== |

||

Revision as of 13:00, 3 April 2014

A multigate device or multiple gate field-effect transistor (MuGFET) refers to a MOSFET (metal–oxide–semiconductor field-effect transistor) which incorporates more than one gate into a single device. The multiple gates may be controlled by a single gate electrode, wherein the multiple gate surfaces act electrically as a single gate, or by independent gate electrodes. A multigate device employing independent gate electrodes is sometimes called a Multiple Independent Gate Field Effect Transistor (MIGFET). Multigate transistors are one of several strategies being developed by CMOS semiconductor manufacturers to create ever-smaller microprocessors and memory cells, colloquially referred to as extending Moore's Law.[1]

Development efforts into multigate transistors have been reported by AMD, Hitachi, IBM, Infineon Technologies, Intel Corporation, TSMC, Freescale Semiconductor, University of California, Berkeley and others and the ITRS predicts that such devices will be the cornerstone of sub-32 nm technologies.[2] The primary roadblock to widespread implementation is manufacturability, as both planar and non-planar designs present significant challenges, especially with respect to lithography and patterning. Other complementary strategies for device scaling include channel strain engineering, silicon-on-insulator-based technologies, and high-k/metal gate materials.

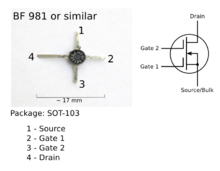

Dual gate MOSFETs are commonly used in VHF mixers and in sensitive VHF front end amplifiers. They are available from manufacturers such as Motorola, NXP, and Hitachi.[3][4][5]

Types

Dozens of multigate transistor variants may be found in the literature. In general, these variants may be differentiated and classified in terms of architecture (planar vs. non-planar design) and number of channels/gates (2, 3, or 4).

Planar double-gate transistor

Planar double-gate transistors employ conventional planar (layer by layer) manufacturing processes to create double-gate devices, avoiding more stringent lithography requirements associated with non-planar, vertical transistor structures. In planar double-gate transistors the drain-source channel is sandwiched between two independently fabricated gate/gate oxide stacks. The primary challenge in fabricating such structures is achieving satisfactory self-alignment between the upper and lower gates.[6]

Flexfet

Flexfet is a planar, independently-double-gated transistor with a damascene metal top gate MOSFET and an implanted JFET bottom gate that are self-aligned in a gate trench. This device is highly scalable due to its sub-lithographic channel length; non-implanted ultra-shallow source and drain extensions; non-epi raised source and drain regions; and gate-last flow. Flexfet is a true double-gate transistor in that (1) both the top and bottom gates provide transistor operation, and (2) the operation of the gates is coupled such that the top gate operation affects the bottom gate operation and vice versa.[7] Flexfet was developed, and is manufactured, by American Semiconductor, Inc.

FinFET

The term FinFET was coined by University of California, Berkeley researchers (Profs. Chenming Hu, Tsu-Jae King-Liu and Jeffrey Bokor) to describe a nonplanar, double-gate transistor built on an SOI substrate,[8] based on the earlier DELTA (single-gate) transistor design.[9] The distinguishing characteristic of the FinFET is that the conducting channel is wrapped by a thin silicon "fin", which forms the body of the device. The thickness of the fin (measured in the direction from source to drain) determines the effective channel length of the device. The Wrap-around gate structure provides a better electrical control over the channel and thus helps in reducing the leakage current and overcoming other short channel effects.

In current usage the term FinFET has a less precise definition. Among microprocessor manufacturers, AMD, IBM, and Freescale describe their double-gate development efforts as FinFET[10] development whereas Intel avoids using the term to describe their closely related tri-gate architecture.[11] In the technical literature, FinFET is used somewhat generically to describe any fin-based, multigate transistor architecture regardless of number of gates.

A 25-nm transistor operating on just 0.7 volt was demonstrated in December 2002 by Taiwan Semiconductor Manufacturing Company. The "Omega FinFET" design is named after the similarity between the Greek letter omega (Ω) and the shape in which the gate wraps around the source/drain structure. It has a gate delay of just 0.39 picosecond (ps) for the N-type transistor and 0.88 ps for the P-type.

FinFET can also have two electrically independent gates, which gives circuit designers more flexibility to design with efficient, low-power gates.[12]

In 2012, Intel started using FinFETs for its future commercial devices. Recent leaks suggest that Intel's FinFET shape has an unusual shape of a triangle rather than rectangle and it is speculated that this might be either because a triangle has a higher structural strength and can be more reliably manufactured or because a triangular prism has a higher area to volume ratio than a rectangular prism thus increasing switching performance.[13]

In September 2012, GlobalFoundries announced plans to offer a 14-nanometer process technology featuring FinFET three-dimensional transistors in 2014.[14] The next month, the rival company TSMC, announced start early or "risk" production of 16 nm FinFETS in November 2013.[15]

In early of 2014, http://www.digitimes.com/news/a20140328PD213.html

Pokud se na 20 nanometrů díváme z hlediska klasických desktopových procesorů a grafických karet, jde ještě o poměrně vzdálenou budoucnost (první produkty očekáváme ve druhé polovině roku - patrně spíš k jejímu konci). Ve sféře mobilních čipů jde ale o přítomnost - například Apple už má čipy A8 od Samsungu i TSMC v rukou minimálně měsíc a nyní probíhají přípravy k sériové výrobě.

I když by se mohlo zdá, že někteří výrobci (resp. designéři) přejdou rovnou na 16 nm, které jsou v těsném závěsu za 20 nm (vypadá to zatím na rozdíl tří kvartálů), bude realita spíše opačná a většina firem zůstane na 20 nm co nejdéle (k podrobnostem se ještě vrátíme). TSMC připravuje následující varianty 16nm výroby: •16nm FinFET - Q4 2014 •16nm FinFET+ - Q4 2014 •16nm FinFET Turbo - 2015-2016

O prvních dvou jsme už měli možnost slyšet. Uvedené datum značí dobu, kdy dojde ke zkušebnímu spuštění linek - v obou případech jde o konec letošního roku. Verze označená plusem by měla nabídnout zhruba o 15 % vyšší rychlost (taktovací frekvenci), přičemž tranzistorová denzita i energetické nároky nebudou negativně ovlivněny.

Plusové varianty, jejíž masová výroba je zatím plánována na samý začátek příštího roku, by měl mezi jinými využít Apple pro SoC generace A9. Třetí varianta s přídomkem Turbo je velkou neznámou. Dozvídáme se o ní poprvé a kromě označení (pravděpodobně jen pracovního), z něhož lze odhadnout cílení na nejvýkonnější segment, o ní nevíme prakticky nic.

16nm proces bude mít smysl pro ty výrobce, pro které je prioritou číslo jedna nízká spotřeba a naopak je netíží finanční stránka. Typickým představitelem takové firmy je Apple, který nemá problém nejdražší výrobní procesy zaplatit, protože produkty na nich postavené snadno a výhodně prodá. Menší firmy naopak zůstanou na 20 nanometrech co to půjde: 16nm výroba (alespoň první dvě verze) nepředstavují výrazné zmenšení čipů, hovoří se o zhruba 5 %. Cenový rozdíl přitom bude několikanásobně vyšší. Pro výrobce, jejichž prioritou je poměr cena/výkon, nebude mít minimálně 6-8 kvartálů přechod na 16 nm smysl.

Podobné to bude i na poli grafických karet a větších procesorů - produkty roku 2015 budou patrně bez výjimky 20nm a nějaké 16nm experimenty určené pro mobilní sféru uvidíme nejdříve v roce 2016, pokud vůbec.

Tri-gate transistor

Tri-gate or 'Transistor (not to be confused with 3D microchips) fabrication is used by Intel Corporation for the nonplanar transistor architecture used in Ivy Bridge and Haswell processors. These transistors employ a single gate stacked on top of two vertical gates allowing for essentially three times the surface area for electrons to travel. Intel reports that their tri-gate transistors reduce leakage and consume far less power than current transistors. This allows up to 37% higher speed, or a power consumption at under 50% of the previous type of transistors used by Intel.[16][17]

Intel explains, "The additional control enables as much transistor current flowing as possible when the transistor is in the 'on' state (for performance), and as close to zero as possible when it is in the 'off' state (to minimize power), and enables the transistor to switch very quickly between the two states (again, for performance)."[18] Intel has stated that all products after Sandy Bridge will be based upon this design.

Intel was the first company to announce this technology. In September 2002,[19] Intel announced their creation of 'Triple-Gate Transistors' to maximize 'transistor switching performance and decreases power-wasting leakage'. A year later in September 2003, AMD announced it was working on similar technology at the International Conference on Solid State Devices and Materials.[20][21] No further announcements of this technology were made until Intel's announcement in May 2011 although it was stated at IDF 2011, that they demonstrated a working SRAM chip based on this technology at IDF 2009.[22]

On April 23, 2012 Intel released a new line of CPUs, termed Ivy Bridge, which feature tri-gate transistors.[23][24] Intel has been working on its tri-gate architecture since 2002, but it took until 2011 to work out mass production issues. The new style of transistor was described on May 4, 2011, in San Francisco.[25] Intel factories are expected to make upgrades over 2011 and 2012 to be able to manufacture the Ivy Bridge CPUs.[26] As well as being used in Intel's Ivy Bridge chips for desktop PCs, the new transistors will also be used in Intel's Atom chips for low powered devices.[25]

The term tri-gate is sometimes used generically to denote any multigate FET with three effective gates or channels.

Gate-all-around (GAA) FET

Gate-all-around FETs are similar in concept to FinFETs except that the gate material surrounds the channel region on all sides. Depending on design, gate-all-around FETs can have two or four effective gates. Gate-all-around FETs have been successfully built around a silicon nanowire.[27] and etched InGaAs nanowires.[28]

Industry need

Planar transistors have been the core of integrated circuits for several decades, during which the size of the individual transistors has steadily decreased. As the size decreases, planar transistors increasingly suffer from the undesirable short-channel effect, especially "off-state" leakage current, which increases the idle power required by the device.[29]

In a multigate device, the channel is surrounded by several gates on multiple surfaces. It thus provides a better electrical control over the channel, allowing more effective suppression of "off-state" leakage current. Multiple gates also allow enhanced current in the "on" state, also known as drive current. Multigate transistors also provide a better analog performance due to a higher intrinsic gain and lower channel length modulation.[30] These advantages translate to lower power consumption and enhanced device performance. Nonplanar devices are also more compact than conventional planar transistors, enabling higher transistor density which translates to smaller overall microelectronics.

Integration challenges

The primary challenges to integrating nonplanar multigate devices into conventional semiconductor manufacturing processes include:

- Fabrication of a thin silicon "fin" tens of nanometers wide

- Fabrication of matched gates on multiple sides of the fin

Compact Modeling

BSIMCMG106.0.0,[31] officially released on March 1, 2012 by UC Berkeley BSIM Group, is the first standard model for FinFETs. BSIM-CMG is implemented in Verilog-A. Physical surface-potential-based formulations are derived for both intrinsic and extrinsic models with finite body doping. The surface potentials at the source and drain ends are solved analytically with poly-depletion and quantum mechanical effects. The effect of finite body doping is captured through a perturbation approach. The analytic surface potential solution agrees closely with the 2-D device simulation results. If the channel doping concentration is low enough to be neglected, computational efficiency can be further improved by a setting a specific flag (COREMOD= 1).

All of the important Multi-Gate (MG) transistor behavior is captured by this model. Volume inversion is included in the solution of Poisson’s equation, hence the subsequent I-V formulation automatically captures the volume inversion effect. Analysis of electro-static potential in the body of MG MOSFETs provided a model equation for short channel effects (SCE). The extra electrostatic control from the end-gates (top/bottom gates) (triple or quadruple-gate) is also captured in the short channel model.

See also

References

- ^ Risch, L. "Pushing CMOS Beyond the Roadmap", Proceedings of ESSCIRC, 2005, p. 63

- ^ Table39b

- ^ "3N201 (Motorola) - Dual Gate Mosfet Vhf Amplifier". Doc.chipfind.ru. Retrieved 2014-03-10.

- ^ "3SK45 datasheet pdf datenblatt - Hitachi Semiconductor - SILICON N-CHANNEL DUAL GATE MOSFET". Alldatasheet.com. Retrieved 2014-03-10.

- ^ http://www.nxp.com/documents/data_sheet/BF1217WR.pdf

- ^ Wong, H-S. Chan, K. Taur, Y. "Self-Aligned (Top and Bottom) Double-Gate MOSFET with a 25 nm Thick Silicon Channel" IEDM 1997, p.427

- ^ Wilson, D.; Hayhurst, R.; Oblea, A.; Parke, S.; Hackler, D. "Flexfet: Independently-Double-Gated SOI Transistor With Variable Vt and 0.5V Operation Achieving Near Ideal Subthreshold Slope" SOI Conference, 2007 IEEE International

- ^ Huang, X. et al. (1999) "Sub 50-nm FinFET: PMOS" International Electron Devices Meeting Technical Digest, p. 67. December 5–8, 1999.

- ^ Hisamoto, D. et al. (1991) "Impact of the vertical SOI 'Delta' Structure on Planar Device Technology" IEEE Trans. Electron. Dev. 41 p. 745.

- ^ "AMD Newsroom". Amd.com. 2014-02-20. Retrieved 2014-03-10.

- ^ "Intel Silicon Technology Innovations". Intel.com. Retrieved 2014-03-10.

- ^ "IEEE Xplore Abstract - Dual- Independent-Gate FinFETs for Low Power Logic Circuits". Ieeexplore.ieee.org. doi:10.1109/TCAD.2010.2097310. Retrieved 2014-03-10.

- ^ "Intel's FinFETs are less fin and more triangle". EE Times. Retrieved 2014-03-10.

- ^ "Globalfoundries looks leapfrog fab rivals with new process". EE Times. Retrieved 2014-03-10.

- ^ "TSMC taps ARM's V8 on road to 16 nm FinFET". EE Times. Retrieved 2014-03-10.

- ^ Cartwright J (2011). "Intel enters the third dimension". Nature. doi:10.1038/news.2011.274.

- ^ Intel to Present on 22-nm Tri-gate Technology at VLSI Symposium (ElectroIQ 2012)

- ^ "Below 22nm, spacers get unconventional: Interview with ASM". ELECTROIQ. Retrieved 2011-05-04.

- ^ http://digidownload.libero.it/kayk/Approfondimenti/Terahertz.pdf

- ^ [1][dead link]

- ^ "AMD Details Its Triple-Gate Transistors". Xbitlabs.com. Retrieved 2014-03-10.

- ^ "IDF 2011: Intel Looks to Take a Bite Out of ARM, AMD With 3D FinFET Tech". DailyTech. Retrieved 2014-03-10.

- ^ Miller, Michael J. PC Magazine http://forwardthinking.pcmag.com/pc-hardware/296972-intel-releases-ivy-bridge-first-processor-with-tri-gate-transistor.

{{cite news}}: Missing or empty|title=(help) - ^ "Intel Reinvents Transistors Using New 3-D Structure". Intel. Retrieved 5 April 2011.

- ^ a b "Transistors go 3D as Intel re-invents the microchip". Ars Technica. 5 May 2011. Retrieved 7 May 2011.

- ^ Murray, Matthew (4 May 2011). "Intel's New Tri-Gate Ivy Bridge Transistors: 9 Things You Need to Know". PC Magazine. Retrieved 7 May 2011.

- ^

Singh N; et al. (2006). "High-Performance fully depleted Silicon Nanowire Gate-All-Around CMOS devices". IEEE Electron Device Letters. 27 (5): 383–386. doi:10.1109/LED.2006.873381.

{{cite journal}}: Explicit use of et al. in:|author=(help) - ^ https://engineering.purdue.edu/~yep/Papers/IEDM_S33P02_GAA_Purdue.pdf

- ^ Subramanian V (2010). "Multiple gate field-effect transistors for future CMOS technologies". IETE Technical Review. 27: 446–454.

- ^ Subramanian (5 Dec 2005). "Device and circuit-level analog performance trade-offs: a comparative study of planar bulk FETs versus FinFETs". Electron Devices Meeting, 2005. IEDM Technical Digest. IEEE International: 898–901.

- ^ "BSIMCMG Model". UC Berkeley.