Interface logic model

This article has multiple issues. Please help improve it or discuss these issues on the talk page. (Learn how and when to remove these messages)

|

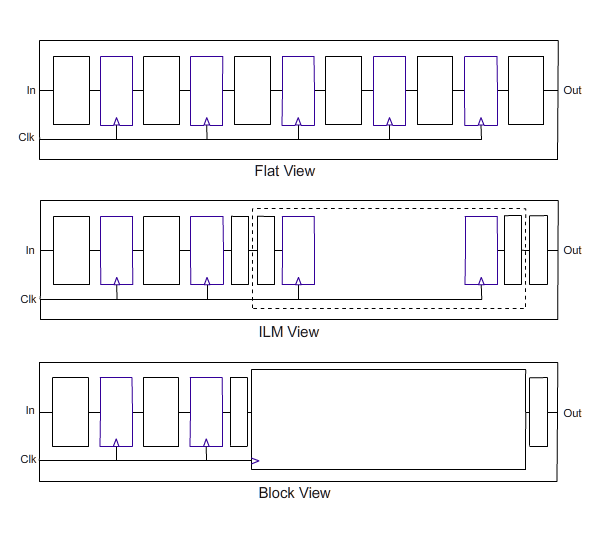

In electronics, the interface logic model (ILM) is a technique to model blocks in hierarchal VLSI implementation flow. It is a gate level model of a physical block where only the connections from the inputs to the first stage of flip-flops, and the connections from the last stage of flip-flops to the outputs are in the model, including the flip-flops and the clock tree driving these flip-flops. All other internal flip-flop to flip-flop paths are stripped out of the ILM.

The advantage of ILM is that the entire path (clock to clock path) is visible at top level for interface nets, unlike traditional block-based hierarchal implementation flow. This gives better accuracy in analysis for interface nets at negligible additional memory and runtime overhead.