Wright etch

The Wright etch (also Wright-Jenkins etch) is a preferential etch for revealing defects in <100>- and <111>-oriented, p- and n-type silicon wafers used for making transistors, microprocessors, memories, and other components. Revealing, identifying, and remedying such defects is essential for progress along the path predicted by Moore's law. It was developed by Margaret Wright Jenkins (1936-2018) in 1976 while working in research and development at Motorola Inc. in Phoenix, AZ. It was published in 1977.[1] This etchant reveals clearly defined oxidation-induced stacking faults, dislocations, swirls and striations with minimum surface roughness or extraneous pitting. These defects are known causes of shorts and current leakage in finished semiconductor devices (such as transistors) should they fall across isolated junctions. A relatively low etch rate (~1 micrometre per minute) at room temperature provides etch control. The long shelf life of this etchant allows the solution to be stored in large quantities.[1]

Etch formula

[edit]The composition of the Wright etch is as follows:

- 60 ml concentrated HF (hydrofluoric acid)

- 30 ml concentrated HNO3 (nitric acid)

- 30 ml of 5 mole CrO3 (mix 1 gram of chromium trioxide per 2 ml of water; the numbers are suspiciously round because the molecular weight of chromium trioxide is almost exactly 100).

- 2 grams Cu(NO3)2 . 3H2O (Copper II Nitrate Trihydrate)

- 60 ml concentrated CH3COOH (acetic acid)

- 60 ml H2O (deionized water)

In mixing the solution, the best results are obtained by first dissolving the copper nitrate in the given amount of water; otherwise the order of mixing is not critical.

Etch mechanism

[edit]The Wright etch consistently produces well-defined etch figures of common defects on silicon surfaces. This effect is attributed to the interactions of the selected chemicals in the formula. Robbins and Schwartz[2][3][4] described chemical etching of silicon in detail using an HF, HNO3 and H2O system; and an HF, HNO3, H2O and CH3COOH (acetic acid) system. Briefly, the etching of silicon is a two-step process. First, the top surface of the silicon is converted into a soluble oxide by a suitable oxidizing agent(s). Then the resulting oxide layer is removed from the surface by dissolution in a suitable solvent, usually HF. This is a continuous process during the etch cycle. In order to delineate a crystal defect, the defect area must be oxidized at a slower or faster rate than the surrounding area thereby forming a mound or pit during the preferential etch process.

In the present system, the silicon is oxidized with HNO3, CrO3 solution (which in this case contains the Cr2O72− dichromate ion, since the pH is low - see the phase diagram in chromic acid) and Cu (NO3)2. The dichromate ion, a strong oxidizing agent, is considered to be the principal oxidizing agent. The ratio of HNO3 to CrO3 solution stated in the formula produces a superior etched surface. Other ratios produce less desirable finishes. With the addition of a small amount of Cu (NO3)2, the definition of the defect was enhanced. Therefore, it is believed that the Cu (NO3)2 affects the localized differential oxidation rate at the defect site. The addition of the acetic acid gave the background surface of the etched silicon a smooth finish. It is theorized that this effect is attributed to the wetting action of the acetic acid which prevents the formation of bubbles during etching.

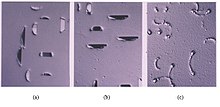

All experimental preferential etching to show defects was done on cleaned and oxidized wafers. All oxidations were performed at 1200 °C in steam for 75 minutes. Figure 1 (a) shows oxidation-induced stacking faults in <100>-oriented wafers after 30 minutes Wright etch, (b) and (c) show dislocation pits on <100>- and <111>-oriented wafers respectively after 20 minutes Wright etch.[1]

Figure 1 (a) shows oxidation-induced stacking faults on a <100>-oriented, 7-10 Ω-cm, boron-doped wafer after 30 minutes Wright etch (the A arrow in this figure points to the shape of faults that intersect the surface, while B points to bulk faults). Figure 1 (b) and (c) show dislocation pits on <100>- and <111>-oriented wafers respectively after 20 minutes Wright etch.[1]

Summary

[edit]This etch process is a quick and reliable method of determining the integrity of pre-processed polished silicon wafers or to reveal defects that may be induced at any point during wafer processing. It has been demonstrated that Wright etch is superior in revealing stacking faults and dislocation etch figures when compared with those revealed by Sirtl[5] and Secco etchings.[6]

This etch is widely used in failure analysis of electrical devices at various wafer processing stages.[7][8] In comparison, the Wright etch was often the preferred etchant to reveal defects in silicon crystals.[7][8]

Figure 2 shows a comparison of oxidation-induced stacking fault delineation on <100>-oriented wafers after Wright etch, Secco and Sirtl etch respectively.[1]

Figure 3 shows a comparison of dislocation pits delineation on <100>-oriented wafers after Wright etch, Secco and Sirtl etch. The final figure 4 shows a comparison of dislocation pits revealed on a <111>-oriented wafer after etching with Wright etch, Secco and Sirtl etch respectively.[1]

Figure 3 shows a comparison of dislocation delineation on a <100>-oriented, 10-20 Ω-cm, boron doped wafer after oxidation and preferential etching. (a) After 20 minutes Wright etch, (b) 10 minutes Secco etch and (c) 6 minutes Sirtl etch.[1]

Figure 4 shows a comparison of dislocation delineation on a <111>-oriented, 10-20 Ω-cm, boron-doped wafer after oxidation and preferential etching. (a) After 10 minutes Wright etch, (b) 10 minutes Secco etch and (c) 3 minutes Sirtl etch. The arrows indicate slip direction.[1]

References

[edit]- ^ a b c d e f g h i j k l Wright Jenkins, Margaret (1977). "A New Preferential Etch for Defects in Silicon Crystals". Journal of the Electrochemical Society. 124 (5): 757–759. Bibcode:1977JElS..124..757W. doi:10.1149/1.2133401. Retrieved 2019-04-06.

- ^ Robbins, Harry; Schwartz, Bertram (1959). "Chemical Etching of Silicon: Part I. The System HF, HNO3, and H2O". Journal of the Electrochemical Society. 106 (6): 505–508. doi:10.1149/1.2427397.

- ^ Robbins, Harry; Schwartz, Bertram (1960). "Chemical Etching of Silicon: Part II. The System HF, HNO3, H2O, and HC2H3O2". Journal of the Electrochemical Society. 107 (2): 108–111. doi:10.1149/1.2427617.

- ^ Robbins, Harry; Schwartz, Bertram (1961). "Chemical Etching of Silicon: Part III. A Temperature Study in the Acid System". Journal of the Electrochemical Society. 108 (4): 365–372. doi:10.1149/1.2428090.

- ^ Sirtl, Erhard; Adler, Annemarie (1961). "Chromsäure-Flussäure als Spezifisches System zur Ätzgrubenentwicklung auf Silizium". Zeitschrift für Metallkunde (in German). 52 (8): 529–534. NAID 10011334657.

- ^ Secco d'Aragona, F. (1972). "Dislocation Etch for (100) Planes in Silicon". Journal of the Electrochemical Society. 119 (7): 948–951. Bibcode:1972JElS..119..948S. doi:10.1149/1.2404374.

- ^ a b Su, Garth K.; Jin, Da; Kim, Sung-Rae; Chan, Tze-Ho; Balan, Hari; Lin, Yung-Tao; Han, Kyung-Joon; Hsia, Steve (2003). "CMOS: Defect Avoidance - Pipeline Defects in Flash Devices Associated with Rings OSF" (PDF). Semiconductor Manufacturing: 144–151. Archived from the original (PDF) on 2016-03-03. Retrieved 2019-04-06.

- ^ a b "Chapter 6". Defect Etching in Silicon. 2002. Archived from the original on 2019-04-06. Retrieved 2019-04-06.