Flash ADC: Difference between revisions

Added Flash Example Picture and Error Correction Info |

|||

| Line 7: | Line 7: | ||

==Implementation== |

==Implementation== |

||

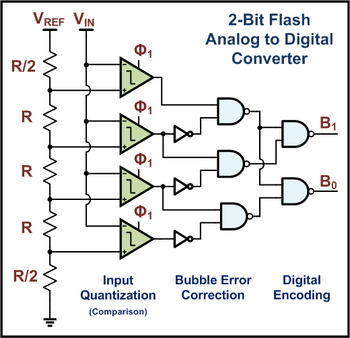

[[File:Flash_ADC.png|thumb|right|350px|A 2-bit Flash ADC Example Implementation with Bubble Error Correction and Digital Encoding]] |

|||

Flash ADCs have been implemented in many technologies, varying from silicon based [[Bipolar junction transistor|bipolar]] (BJT) and complementary metal oxide [[field effect transistor|FETs]] (CMOS) technologies to rarely used [[List of semiconductor materials|III-V]] technologies. Often this type of ADC is used as a first medium sized analog circuit verification. |

Flash ADCs have been implemented in many technologies, varying from silicon based [[Bipolar junction transistor|bipolar]] (BJT) and complementary metal oxide [[field effect transistor|FETs]] (CMOS) technologies to rarely used [[List of semiconductor materials|III-V]] technologies. Often this type of ADC is used as a first medium sized analog circuit verification. |

||

| Line 14: | Line 16: | ||

Recently, offset calibration has been introduced in the flash ADC designs. Instead of properly designing the analog circuit (which actually means increasing the components sizes to suppress variation) the offset is removed during use. A test signal is applied and each the offset of each comparator is calibrated to below the LSB size of the ADC. Due to the heavy calibration effort the design are up to now always limited to 4-bits. |

Recently, offset calibration has been introduced in the flash ADC designs. Instead of properly designing the analog circuit (which actually means increasing the components sizes to suppress variation) the offset is removed during use. A test signal is applied and each the offset of each comparator is calibrated to below the LSB size of the ADC. Due to the heavy calibration effort the design are up to now always limited to 4-bits. |

||

Another recent improvement to many flash ADCs is the inclusion of error correction. When the ADC is used to harsh environments or constructed in very small integrated circuit processes, there is a heightened risk of a comparator randomly outputting a wrong code. Bubble error correction is a digital correction mechanism that will prevent a comparator that has tripped high from outputting a high code if it is surrounded by comparators that have not tripped high. |

|||

==Folding ADC== |

==Folding ADC== |

||

Revision as of 04:07, 13 December 2009

A Flash ADC (also known as a Direct conversion ADC) is a type of analog-to-digital converter that uses a linear voltage ladder with a comparator at each "rung" of the ladder to compare the input voltage to successive reference voltages. Often these reference ladders are constructed of many resistors; however modern implementations show that also capacitive voltage division is possible. The output of these comparators is generally fed into a digital encoder which converts the inputs into a binary value (the collected outputs from the comparators can be thought of as a unary value).

Benefits and drawbacks

Flash converters are extremely fast compared to many other types of ADCs which usually narrow in on the "correct" answer over a series of stages. Compared to these, a Flash converter is also quite simple and, apart from the analog comparators, only requires logic for the final conversion to binary.

A Flash converter requires a huge number of comparators compared to other ADCs, especially as the precision increases. A Flash converter requires comparators for an n-bit conversion. The size and cost of all those comparators makes Flash converters generally impractical for precisions much greater than 8 bits (255 comparators). In place of these comparators, most other ADCs substitute more complex logic which can be scaled more easily for increased precision.

Implementation

Flash ADCs have been implemented in many technologies, varying from silicon based bipolar (BJT) and complementary metal oxide FETs (CMOS) technologies to rarely used III-V technologies. Often this type of ADC is used as a first medium sized analog circuit verification.

The earliest implementations consisted of a reference ladder of well matched resistors connected to a reference voltage. Each tap at the resistor ladder is used for one comparator, possibly preceded by an amplification stage, and thus generates a logical '0' or '1' depending if the measured voltage is above or below the reference voltage of the resistor tap. The reason to add an amplifier is twofold: it amplifies the voltage difference and therefore suppresses the comparator offset, and the kick-back noise of the comparator towards the reference ladder is also strongly suppressed. Typically designs from 4-bit up to 6-bit, and sometimes 7-bit are produced.

Designs with power-saving capacitive reference ladders have been demonstrated. In addition to clocking the comparator(s), these systems also sample the reference value on the input stage. As the sampling is done at a very high rate, the leakage of the capacitors is negligible.

Recently, offset calibration has been introduced in the flash ADC designs. Instead of properly designing the analog circuit (which actually means increasing the components sizes to suppress variation) the offset is removed during use. A test signal is applied and each the offset of each comparator is calibrated to below the LSB size of the ADC. Due to the heavy calibration effort the design are up to now always limited to 4-bits.

Another recent improvement to many flash ADCs is the inclusion of error correction. When the ADC is used to harsh environments or constructed in very small integrated circuit processes, there is a heightened risk of a comparator randomly outputting a wrong code. Bubble error correction is a digital correction mechanism that will prevent a comparator that has tripped high from outputting a high code if it is surrounded by comparators that have not tripped high.

Folding ADC

The number of comparators can be reduced somewhat by adding a folding circuit in front, making a so called folding ADC. Instead of using the comparators in a Flash ADC only once, during a ramp input signal, the folding ADC re-uses the comparators multiple times. If a m-times folding circuit is used in an n-bit ADC, the actual number of comparator can be reduced from to (there is always one needed to detect the range crossover). Typical folding circuits are, e.g., the Gilbert multiplier, or analog wired-or circuits.

Application

The very high sample rate of this type of ADC enable Gigahertz applications like radar detection, wide band radio receivers and optical communication links. More often the flash ADC is embedded in a large IC containing many digital decoding functions. Also a small flash ADC circuit may be present inside a Delta-sigma modulation loop.

See also

References

- Analog to Digital Conversion

- Understanding Flash ADCs

- "Integrated Analog-to-Digital and Digital-to-Analog Converters ", R. van de Plassche, ADCs, Kluwer Academic Publishers, 1994.

- "A Precise Four-Quadrant Multiplier with Subnanosecond Response", Barrie Gilbert, IEEE Journal of Solid-State Circuits, Vol. 3, No. 4 (1968), pp. 365-373