Four-phase logic

Four-phase logic is a type of, and design methodology for, dynamic logic. It enabled non-specialist engineers to design quite complex ICs, using either PMOS or NMOS processes. It uses a kind of 4-phase clock signal.

History

R. K. "Bob" Booher, an engineer at Autonetics, invented four-phase logic, and communicated the idea to Frank Wanlass at Fairchild Semiconductor; Wanlass promoted this logic form at General Instrument Microelectronics Division.[1] Booher made the first working four-phase chip, the Autonetics DDA integrator, during February 1966; he later designed several chips for and built the Autonetics D200 airborne computer using this technique.[2]

In April 1967, Joel Karp and Elizabeth de Atley published an article "Use four-phase MOS IC logic" in Electronic Design magazine.[3] In the same year, Cohen, Rubenstein, and Wanlass published "MTOS four phase clock systems."[4] Wanlass had been director of research and engineering at General Instrument Microelectronics Division in New York since leaving Fairchild Semiconductor in 1964.

Lee Boysel, a disciple of Wanlass[5] and a designer at Fairchild Semiconductor, and later founder of Four-Phase Systems, gave a "late news" talk on a four-phase 8-bit adder device in October 1967 at the International Electron Devices meeting.[6] J. L. Seely, manager of MOS Operations at General Instrument Microelectronics Division, also wrote about four-phase logic in late 1967.[7]

In 1968 Boysel published an article "Adder On a Chip: LSI Helps Reduce Cost of Small Machine" in Electronics magazine;[8] Four-phase papers from Y. T. Yen also appear that year.[9][10] Other papers followed shortly.[11]

Boysel recalls that four-phase dynamic logic allowed him to achieve 10X the packing density, 10X the speed, and 1/10 the power, compared to other MOS techniques being used at the time (metal-gate saturated-load PMOS logic), using the first-generation MOS process at Fairchild.[12]

Structure

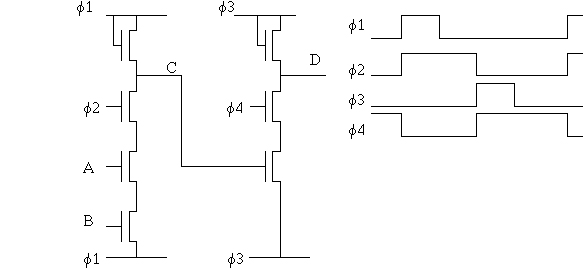

There are basically two types of logic gate – a '1' gate and a '3' gate. These differ only in the clock phases used to drive them. A gate can have any logic function; thus potentially each and every gate has a customized layout. An example 2-input NAND 1 gate and an inverter 3 gate, together with their clock phases (the example uses NMOS transistors), are shown below:

The ø1 and ø3 clocks need to be non-overlapping, as do the ø2 and ø4 clocks. Considering the 1 gate, during the ø1 clock high time (also known as the precharge time) the output C precharges up to V(ø1)−Vth, where Vth represents the threshold of the precharge transistor. During the next quarter clock cycle (the sample time), when ø1 is low and ø2 is high, C either stays high (if A or B are low) or C gets discharged low (if A and B are high).

The A and B inputs must be stable throughout this sample time. The output C becomes valid during this time – and therefore a 1 gate output can't drive another 1 gate's inputs. Hence 1 gates have to feed 3 gates and they in turn have to feed 1 gates.

One more thing is useful – 2 and 4 gates. A 2 gate precharges on ø1 and samples on ø3:

and a 4 gate precharges on ø3 and samples on ø1.

Gate interconnection rules are: 1 gates can drive 2 gates and/or 3 gates; 2 gates can drive only 3 gates, 3 gates can drive 4 gates and/or 1 gates, 4 gates can drive only 1 gates:

Usage

Four-phase logic works well; in particular there are no race hazards because every combinational logic gate includes a register. It's worth noting that the layout does not require the bussing of any power supplies – only clock lines are bussed. Also, since the design technique is ratioless (cf. static logic), many designs can use minimum-size transistors.

There are some difficulties:

- The gate output is dynamic. This means that its state is held on capacitance at the gate output. But the output track can cross clock lines and other gate outputs, all of which can change the charge on the capacitor. In order that the gate output voltage remains at some safe 0 or 1 level during the cycle the amount of change has to be calculated and, if necessary, additional (diffusion) capacitance has to be added to the output node.

- For a given supply voltage, process, and clock frequency, the designer has to do some calculations so that the layout engineers can, in turn, do their calculations to work out the 'bulk-up' capacitance needed for each gate. A gate with a lot of capacitance load could need bigger than minimum input transistors (in order that the load could be discharged in time). This in turn increases the load on the gates driving that gate's inputs. So it can happen, especially in high-frequency designs, that the gate sizing keeps on increasing if the speed target is too aggressive.

Evolution

With the advent of CMOS, the precharge transistor could be changed to be the complement of the logic transistor type, which allows the gate's output to charge quickly all the way up to the high level of the clock line, thus improving the speed, signal swing, power consumption, and noise margin. This technique is used in domino logic.

References

- ^ Ross Knox Bassett (2007). To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology. JHU Press. pp. 129–130. ISBN 978-0-8018-8639-3.

- ^ R. K. Booher, "MOS GP Computer," afips, pp.877, 1968 Proceedings of the Fall Joint Computer Conference, 1968

- ^

Bernard Finn, Robert Bud, Helmuth Trischler (2000). Exposing electronics. CRC Press. p. 133. ISBN 978-90-5823-057-7.

{{cite book}}: CS1 maint: multiple names: authors list (link) - ^

L. Cohen, R. Rubenstin, and F. Wanlass (1–3 November 1967), "MTOS four phase clock systems", Northeast Electronics Research and Engineering Meeting (NEREM) Record, vol. 9, pp. 170–171

{{citation}}: CS1 maint: multiple names: authors list (link) - ^ Ross Knox Bassett (2007). To the Digital Age: Research Labs, Start-up Companies, and the Rise of MOS Technology. JHU Press. p. 122. ISBN 978-0-8018-8639-3.

- ^

L. Boysel, J. Kelley, and R. Cole (October 1967), "MOS/LSI 8-Bit Parallel Accumulator", International Electron Devices Meeting (IEDM), pp. 2–3

{{citation}}: CS1 maint: multiple names: authors list (link) - ^ J. L. Seely (March 1967). "Advances in the state-of-the-art of MOS device technology". Solid State Technology. 10: 55–62.

- ^ Lee L. Boysel (18 March 1968). "Adder on a Chip: LSI Helps Reduce Cost of Small Machine". Electronics. 18: 119–123.

- ^ Y. T. Yen (1968) "A Mathematical Model Characterizing Four-Phase MOS Circuits for Logic Simulation" IEEE Transactions on Computers: C-17 Sept. 1968

- ^ Y. T. Yen (1968) "Intermittent Failure Problems of Four-Phase MOS Circuits" IEEE Journal of Solid-State Circuits: SC-4 No. 3 June. 1969

- ^ Hatt R. J., Jackets A. E. & Jarvis D. B. of Associated Semiconductor Manufacturers "Four-phase Logic Circuits using Integrated m-o-s Transistors" Mullard Technical Communication: No 99 May 1969

- ^ Lee Boysel (10/12/2007). "Making Your First Million (and other tips for aspiring entrepreneurs)". U. Mich. EECS Presentation / ECE Recordings.

{{cite web}}: Check date values in:|date=(help)