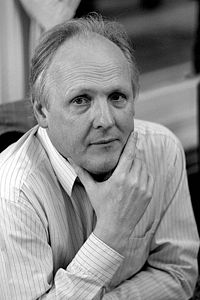

Steve Furber

Steve Furber | |

|---|---|

Steve Furber | |

| Born | Stephen Byram Furber 21 March 1953[59] |

| Nationality | British |

| Alma mater |

|

| Known for | |

| Awards | |

| Scientific career | |

| Fields | |

| Institutions | |

| Thesis | Is the Weis-Fogh principle exploitable in turbomachines? (1979) |

| Doctoral advisor | John Ffowcs Williams[7] |

| Doctoral students |

|

| Other notable students | Simon Segars (CEO of ARM)[57] |

| Website | apt manchester |

Stephen Byram "Steve" Furber CBE, FRS, FREng[64] (born 21 March 1953) is the ICL Professor of Computer Engineering at the School of Computer Science at the University of Manchester[65] and is probably best known for his work at Acorn Computers, where he was one of the designers of the BBC Micro and the ARM 32-bit RISC microprocessor.[6][63][66][67][68][69][70][71][72][58]

Education

Furber was educated at Manchester Grammar School and represented the UK in the International Mathematical Olympiad in Hungary in 1970 and won a bronze medal.[73] He went on to study the Cambridge Mathematical Tripos at St John's College, Cambridge, receiving a Bachelor of Arts degree in mathematics in 1974. In 1978, he was appointed the Rolls-Royce Research Fellow in Aerodynamics at Emmanuel College, Cambridge and was awarded a PhD in 1980 on the fluid dynamics of the Weis-Fogh principle.[74][75]

Acorn Computers, BBC Micro and ARM

From 1980 to 1990, Furber worked at Acorn Computers where he was a Hardware Designer and then Design Manager. He was a principal designer of the BBC Micro and the ARM microprocessor. In August 1990 he moved to the University of Manchester to become the ICL Professor of Computer Engineering and established the Amulet research group.

Research

In 2003, Furber was a member of the EPSRC research cluster in biologically-inspired[76] novel computation. On 16 September 2004, he gave a speech on Hardware Implementations of Large-scale Neural Networks as part of the initiation activities of the Alan Turing Institute.

Furber's latest project is known as SpiNNaker (Spiking Neural Network Architecture),[61] [77][78][79][80] also nicknamed the "brain box", to be constructed at the University of Manchester. This is an attempt to build a new kind of computer that directly mimics the workings of the human brain. Spinnaker is essentially an artificial neural network realised in hardware, a massively parallel processing system eventually designed to incorporate a million ARM processors.[81][82] The finished Spinnaker will model 1 per cent of the human brain's capability, or around 1 billion neurons. The Spinnaker project[83] aims amongst other things to investigate:

- How can massively parallel computing resources accelerate our understanding of brain function?

- How can our growing understanding of brain function point the way to more efficient parallel, fault-tolerant computation?

Furber believes that "significant progress in either direction will represent a major scientific breakthrough".[83]

Furber's research interests include asynchronous systems, ultra-low-power processors for sensor networks, on-chip interconnect and globally asynchronous locally synchronous (GALS),[84] and neural systems engineering.[85][86][87][88]

Awards and honours

A significant part of Furber's research is funded by grants that have been awarded by the EPSRC.[89] In February 1997, Furber was elected a Fellow of the British Computer Society. In 1998, he became a member of the European Working Group on Asynchronous Circuit Design (ACiD-WG). He was elected a Fellow of the Royal Society (FRS) in 2002[90] and was Specialist Adviser to the House of Lords Science and Technology Select Committee inquiry into microprocessor technology.

Furber is a Fellow[64] of the Royal Academy of Engineering,[64] the IEEE (2005) and the IET, and is a Chartered Engineer. In September 2007 he was awarded the prestigious IET Faraday Medal. In 2010 he gave the IET Pinkerton Lecture.

Furber was appointed Commander of the Order of the British Empire (CBE) in the 2008 New Year Honours[91][92] and was elected as one of the three laureates of Millennium Technology Prize in 2010 (with Richard Friend and Michael Grätzel), for development of ARM processor.[93]

In 2012, Furber was made a Fellow of the Computer History Museum "for his work, with Sophie Wilson, on the BBC Micro computer and the ARM processor architecture."[94][95]

In 2014, he was made a Distinguished Fellow at the British Computer Society (DFBCS) recognising his contribution to the IT profession and industry, joining the likes of Bill Gates, Tim Berners Lee, Vint Cerf and Tom Kilburn.[4]

Furber's nomination for the Royal Society reads:

Professor Furber is distinguished for his fundamental contributions to the design and analysis of electronic systems, especially microprocessors. He was the original designer of the hardware architecture of the ARM processor, the world's leading embedded processor core and a major engineering and commercial success for the United Kingdom. Having moved to Manchester University, he established a research team to investigate asynchronous processor design, which rapidly made fundamental contributions to the field. He has shown how to combine academic design theories with practical engineering constraints to achieve a remarkable and elegant synthesis. His work demonstrates in particular how to design microprocessors with low power and low radio frequency emissions, necessary for future wireless applications. Furber has designed a series of highly original asynchronous processors to execute the ARM instruction set. These have been fabricated and subjected to extensive experimental analysis. Furber's group is the world's leading centre of research in both fundamental theory and engineering implementation of such devices.[1]

Furber was played by actor Sam Philips in the BBC Four documentary drama Micro Men,[96] first aired on 8 October 2009.

Personal life

Furber is married to Valerie Elliot with two daughters[59] and plays 6-string and bass guitar.[citation needed]

References

- ^ a b "Library and Archive Catalogue EC/2002/10: Furber, Stephen Byram". London: The Royal Society. Archived from the original on 17 March 2014.

- ^ Steve Furber 2012 Fellow

- ^ BCS Lovelace Medal

- ^ a b Sarah Chatwin (14 March 2014). "Professor Steve Furber – BCS Distinguished Fellow". [Computer Science Manchester]. Retrieved 14 March 2014.

- ^ Monroe, D. (2014). "Neuromorphic computing gets ready for the (really) big time". Communications of the ACM. 57 (6): 13–15. doi:10.1145/2601069.

- ^ a b Steve Furber publications indexed by Google Scholar

- ^ Steve Furber at the Mathematics Genealogy Project

- ^ Bainbridge, W. J.; Furber, S. B. (2001). "Delay insensitive system-on-chip interconnect using 1-of-4 data encoding". Proceedings Seventh International Symposium on Asynchronous Circuits and Systems. ASYNC 2001. p. 118. doi:10.1109/ASYNC.2001.914075. ISBN 0-7695-1034-5.

- ^ Bainbridge, J.; Furber, S. (2002). "Chain: A delay-insensitive chip area interconnect". IEEE Micro. 22 (5): 16. doi:10.1109/MM.2002.1044296.

- ^ Bainbridge, William John (2000). Asynchronous system-on-chip interconnect (PhD thesis). University of Manchester (CPHC/BCS distinguished dissertation winner). ISBN 9781852335984.

- ^ Bose, J.; Furber, S. B.; Shapiro, J. L. (2005). "An associative memory for the on-line recognition and prediction of temporal sequences". Proceedings. 2005 IEEE International Joint Conference on Neural Networks, 2005. Vol. 2. p. 1223. doi:10.1109/IJCNN.2005.1556028. ISBN 0-7803-9048-2.

- ^ Bose, Joy (2007). Engineering a sequence machine through spiking neurons employing rank-order codes (PhD thesis). University of Manchester.

- ^ Davies, S.; Galluppi, F.; Rast, A. D.; Furber, S. B. (2012). "A forecast-based STDP rule suitable for neuromorphic implementation". Neural Networks. 32: 3–14. doi:10.1016/j.neunet.2012.02.018. PMID 22386500.

- ^ Davies, Sergio (2013). Learning in Spiking Neural Networks (PhD thesis). University of Manchester.

- ^ Emmons, Christopher Daniel (2010). Exploiting concurrency in a general purpose one-instruction computer architecture (PhD thesis). University of Manchester.

- ^ Endecott, Philip Brian (1996). SCALP: a superscalar asynchronous low-power processor (PhD thesis). University of Manchester.

- ^ Felicijan, T.; Furber, S. B. (2004). "An asynchronous on-chip network router with quality-of-service (QoS) support". IEEE International SOC Conference, 2004. Proceedings. p. 274. doi:10.1109/SOCC.2004.1362432. ISBN 0-7803-8445-8.

- ^ Felicijan, Tomaz (2004). Quality-of-Service (QoS) for asynchronous On-Chip Networks (PhD thesis). University of Manchester.

- ^ Galluppi, Francesco (2013). Information Representation on a Universal Neural Chip (PhD thesis). University of Manchester.

- ^ Galluppi, F.; Davies, S.; Rast, A.; Sharp, T.; Plana, L. A.; Furber, S. (2012). "A hierachical [sic] configuration system for a massively parallel neural hardware platform". Proceedings of the 9th conference on Computing Frontiers - CF '12. p. 183. doi:10.1145/2212908.2212934. ISBN 9781450312158.

- ^ Rast, A.; Galluppi, F.; Davies, S.; Plana, L.; Patterson, C.; Sharp, T.; Lester, D.; Furber, S. (2011). "Concurrent heterogeneous neural model simulation on real-time neuromimetic hardware". Neural Networks. 24 (9): 961–978. doi:10.1016/j.neunet.2011.06.014. PMID 21778034.

- ^ Grymel, Martin Thomas (2013). Error Control With Binary Cyclic Codes (PhD thesis). University of Manchester.

- ^ Grymel, M.; Furber, S. B. (2011). "A Novel Programmable Parallel CRC Circuit". IEEE Transactions on Very Large Scale Integration (VLSI) Systems. 19 (10): 1898. doi:10.1109/TVLSI.2010.2058872.

- ^ Hormdee, D.; Garside, J. D.; Furber, S. B. (2003). "An asynchronous copy-back cache architecture". Microprocessors and Microsystems. 27 (10): 485. doi:10.1016/S0141-9331(03)00101-7.

- ^ Hormdee, Daranee (2002). Copy-back cache organisation for an asynchronous microprocessor (PhD thesis). University of Manchester.

- ^ Xin Jin; Lujan, M.; Plana, L. A.; Davies, S.; Temple, S.; Furber, S. B. (2010). "Modeling Spiking Neural Networks on SpiNNaker". Computing in Science & Engineering. 12 (5): 91. doi:10.1109/MCSE.2010.112.

- ^ Jin, Xin (2010). Parallel simulation of neural networks on SpiNNaker universal neuromorphic hardware (PhD thesis). University of Manchester.

- ^ Khan, M. M.; Lester, D. R.; Plana, L. A.; Rast, A.; Jin, X.; Painkras, E.; Furber, S. B. (2008). "SpiNNaker: Mapping neural networks onto a massively-parallel chip multiprocessor". 2008 IEEE International Joint Conference on Neural Networks (IEEE World Congress on Computational Intelligence). p. 2849. doi:10.1109/IJCNN.2008.4634199. ISBN 978-1-4244-1820-6.

- ^ Khan, Muhammad Mukaram (2009). Configuring a massively parallel CMP system for real-time neural applications (PhD thesis). University of Manchester.

- ^ Liu, Jianwei (1997). Arithmetic and control components for an asynchronous system (PhD thesis). University of Manchester.

- ^ Yijun Liu; Furber, S. (2005). "A Low Power Embedded Dataflow Coprocessor". IEEE Computer Society Annual Symposium on VLSI: New Frontiers in VLSI Design (ISVLSI'05). p. 246. doi:10.1109/ISVLSI.2005.9. ISBN 0-7695-2365-X.

- ^ Liu, Yijun (2005). Power-efficient embedded processing (PhD thesis). University of Manchester.

- ^ Okoyo, Henry Okora (1998). A synaptic logic neuron model (PhD thesis). University of Manchester.

- ^ Painkras, Eustace (2013). A chip multiprocessor for a large-scale neural simulator (PhD thesis). University of Manchester.

- ^ Patterson, C.; Garside, J.; Painkras, E.; Temple, S.; Plana, L. A.; Navaridas, J.; Sharp, T.; Furber, S. (2012). "Scalable communications for a million-core neural processing architecture". Journal of Parallel and Distributed Computing. 72 (11): 1507. doi:10.1016/j.jpdc.2012.01.016.

- ^ Painkras, E.; Plana, L. A.; Garside, J.; Temple, S.; Davidson, S.; Pepper, J.; Clark, D.; Patterson, C.; Furber, S. (2012). "SpiNNaker: A multi-core System-on-Chip for massively-parallel neural net simulation". Proceedings of the IEEE 2012 Custom Integrated Circuits Conference. p. 1. doi:10.1109/CICC.2012.6330636. ISBN 978-1-4673-1556-2.

- ^ Woods, J. V.; Day, P.; Furber, S. B.; Garside, J. D.; Paver, N. C.; Temple, S. (1997). "AMULET1: An asynchronous ARM microprocessor". IEEE Transactions on Computers. 46 (4): 385. doi:10.1109/12.588033.

- ^ Paver, Nigel Charles (1994). The design and implementation of an asynchronous microprocessor (PhD thesis). University of Manchester.

- ^ Petlin, O. A.; Furber, S. B. (1995). "Scan testing of asynchronous sequential circuits". Proceedings. Fifth Great Lakes Symposium on VLSI. p. 224. doi:10.1109/GLSV.1995.516057. ISBN 0-8186-7035-5.

- ^ Petlin, Oleg Alexandrovich (1996). Design for testability of asynchronous VLSI circuits (PhD thesis). University of Manchester.

- ^ Patterson, C.; Preston, T.; Galluppi, F.; Furber, S. (2012). "Managing a Massively-Parallel Resource-Constrained Computing Architecture". 2012 15th Euromicro Conference on Digital System Design. p. 723. doi:10.1109/DSD.2012.84. ISBN 978-0-7695-4798-5.

- ^ Patterson, James Cameron (2012). Managing a real-time massively-parallel neural architecture (PhD thesis). University of Manchester.

- ^ Rast, A. D.; Shufan Yang; Khan, M.; Furber, S. B. (2008). "Virtual synaptic interconnect using an asynchronous network-on-chip". 2008 IEEE International Joint Conference on Neural Networks (IEEE World Congress on Computational Intelligence). p. 2727. doi:10.1109/IJCNN.2008.4634181. ISBN 978-1-4244-1820-6.

- ^ Rast, Alexander (2011). Scalable event-driven modelling architectures for neuromimetic hardware (PhD thesis). University of Manchester.

- ^ Bhattacharya, B. S.; Furber, S. B. (2010). "Biologically Inspired Means for Rank-Order Encoding Images: A Quantitative Analysis". IEEE Transactions on Neural Networks. 21 (7): 1087–1099. doi:10.1109/TNN.2010.2048339. PMID 20550988.

- ^ Sen, B.; Furber, S. (2009). "Evaluating rank-order code performance using a biologically-derived retinal model". 2009 International Joint Conference on Neural Networks. p. 2867. doi:10.1109/IJCNN.2009.5178842. ISBN 978-1-4244-3548-7.

- ^ Sen, Basabdatta (2008). Information recovery from rank-order encoded images (PhD thesis). University of Manchester.

- ^ Sharp, Tom (2013). Real-Time Million-Synapse Simulation of Cortical Tissue (PhD thesis). University of Manchester.

- ^ Sharp, T.; Patterson, C.; Furber, S. (2011). "Distributed configuration of massively-parallel simulation on SpiNNaker neuromorphic hardware". The 2011 International Joint Conference on Neural Networks. p. 1099. doi:10.1109/IJCNN.2011.6033346. ISBN 978-1-4244-9635-8.

- ^ Sharp, T.; Galluppi, F.; Rast, A.; Furber, S. (2012). "Power-efficient simulation of detailed cortical microcircuits on SpiNNaker". Journal of Neuroscience Methods. 210 (1): 110–118. doi:10.1016/j.jneumeth.2012.03.001. PMID 22465805.

- ^ Shi, Y.; Furber, S. B.; Garside, J.; Plana, L. A. (2009). "Fault Tolerant Delay Insensitive Inter-chip Communication". 2009 15th IEEE Symposium on Asynchronous Circuits and Systems. p. 77. doi:10.1109/ASYNC.2009.21. ISBN 978-0-7695-3616-3.

- ^ Shi, Yebin (2010). Fault-tolerant delay-insensitive communication (PhD thesis). University of Manchester.

- ^ Wu, J.; Furber, S. (2009). "A Multicast Routing Scheme for a Universal Spiking Neural Network Architecture". The Computer Journal. 53 (3): 280. doi:10.1093/comjnl/bxp024.

- ^ Wu, Jian (2010). Router for massively-parallel neural simulation (PhD thesis). University of Manchester.

- ^ Yang, Shufan (2010). Memory interconnect management on a chip multiprocessor (PhD thesis). University of Manchester.

- ^ Yu, Zongchuan (2004). Investigation into the security of self-timed circuits (PhD thesis). University of Manchester.

- ^ Segars, Simon Anthony (1996). Low power microprocessor design (MSc thesis). University of Manchester.

- ^ a b National Life Stories, Professor Steve Furber Interviewed by Thomas Lean, British Library

- ^ a b c FURBER. "FURBER, Prof. Stephen Byram". Who's Who. Vol. 2015 (online Oxford University Press ed.). A & C Black.

{{cite encyclopedia}}: Unknown parameter|othernames=ignored (help) (Subscription or UK public library membership required.) (subscription required) - ^ Brown, David (1 February 2010). "A Conversation with Steve Furber". Queue. Association for Computing Machinery. Retrieved 7 March 2012.

- ^ a b Furber, S. B.; Galluppi, F.; Temple, S.; Plana, L. A. (2014). "The SpiNNaker Project". Proceedings of the IEEE: 1. doi:10.1109/JPROC.2014.2304638.

- ^ "The Human Brain Project SP 9: Neuromorphic Computing Platform" on YouTube

- ^ a b Furber, Stephen B. (2000). ARM system-on-chip architecture. Boston: Addison-Wesley. ISBN 0-201-67519-6.

- ^ a b c "List of Fellows".

- ^ "Prof Stephen Furber (CBE FRS FREng FBCS FIET CITP CEng), research profile – personal details (The University of Manchester)". Retrieved 11 June 2012.

- ^ Steve Furber publications indexed by Microsoft Academic

- ^ Stephen B. Furber at DBLP Bibliography Server

- ^ Furber, Stephen B. (1989). VLSI RISC architecture and organization. New York: M. Dekker. ISBN 0-8247-8151-1.

- ^ Steve Furber's publications indexed by the Scopus bibliographic database. (subscription required)

- ^ Grier, D. A. (2014). "Steve Furber [Interviews]". IEEE Annals of the History of Computing. 36: 58. doi:10.1109/MAHC.2014.8.

- ^ Lean, Thomas (22 October 2012). "Steve Furber: developing ARM with no people and no money". British Library.

- ^ ARM and its Partners talk about reaching the 50 Billion chip milestone on YouTube

- ^ Steve Furber's results at International Mathematical Olympiad

- ^ Furber, S. B.; Williams, J. E. F. (1979). "Is the Weis-Fogh principle exploitable in turbomachinery?". Journal of Fluid Mechanics. 94 (3): 519. doi:10.1017/S0022112079001166.

- ^ Fitzpatrick, J. (2011). "An interview with Steve Furber". Communications of the ACM. 54 (5): 34. doi:10.1145/1941487.1941501.

- ^ Furber, S. (2006). "Living with Failure: Lessons from Nature?". Eleventh IEEE European Test Symposium (ETS'06). pp. 4–0. doi:10.1109/ETS.2006.28. ISBN 0-7695-2566-0.

- ^ Professor Steve Furber: Building brains on YouTube

- ^ Professor Steve Furber Introduces SpiNNaker on YouTube

- ^ Xin Jin; Furber, S. B.; Woods, J. V. (2008). "Efficient modelling of spiking neural networks on a scalable chip multiprocessor". 2008 IEEE International Joint Conference on Neural Networks (IEEE World Congress on Computational Intelligence). pp. 2812–2819. doi:10.1109/IJCNN.2008.4634194. ISBN 978-1-4244-1820-6.

- ^ Dempsey, Paul (15 March 2011). "SpiNNaker set to receive new 18-core SoC to help reverse engineer the human brain". Engineering and Technology Magazine. Institution of Engineering and Technology. Retrieved 7 March 2012.

- ^ Bush, Steve (8 July 2011). "One million ARM cores to simulate brain at Manchester". Electronics Weekly. Retrieved 11 July 2011.

UK scientists aim to model 1 per cent of a human brain with up to one million ARM cores. ... ARM was approached in May 2005 to participate in SpiNNaker ... agreement extends to Manchester making enough chips for a computer with a million cores.

- ^ "Acorn's Steve Furber looks to ARM supercomputers: A million node supercomputer". Techgineering. techgineering.org. 8 July 2011. Retrieved 7 March 2012.

- ^ a b Furber, S. (2011). "Biologically-Inspired Massively-Parallel Architectures: A Reconfigurable Neural Modelling Platform" (PDF). 6578: 2–2. doi:10.1007/978-3-642-19475-7_2.

{{cite journal}}: Cite journal requires|journal=(help) - ^ Plana, L. A.; Furber, S. B.; Temple, S.; Khan, M.; Shi, Y.; Wu, J.; Yang, S. (2007). "A GALS Infrastructure for a Massively Parallel Multiprocessor". IEEE Design & Test of Computers. 24 (5): 454. doi:10.1109/MDT.2007.149.

- ^ Temple, S.; Furber, S. (2007). "Neural systems engineering". Journal of the Royal Society Interface. 4 (13): 193. doi:10.1098/rsif.2006.0177.

- ^ Sharp, T; Petersen, R; Furber, S (2014). "Real-time million-synapse simulation of rat barrel cortex". Frontiers in Neuroscience. 8: 131. doi:10.3389/fnins.2014.00131. PMC 4038760. PMID 24910593.

{{cite journal}}: CS1 maint: unflagged free DOI (link) - ^ Bhattacharya, B. S.; Patterson, C; Galluppi, F; Durrant, S. J.; Furber, S (2014). "Engineering a thalamo-cortico-thalamic circuit on SpiNNaker: A preliminary study toward modeling sleep and wakefulness". Frontiers in Neural Circuits. 8: 46. doi:10.3389/fncir.2014.00046. PMC 4033042. PMID 24904294.

{{cite journal}}: CS1 maint: unflagged free DOI (link) - ^ Cumming, D. R.; Furber, S. B.; Paul, D. J. (2014). "Beyond Moore's law". Philosophical Transactions of the Royal Society A: Mathematical, Physical and Engineering Sciences. 372 (2012): 20130376. Bibcode:2014RSPTA.37230376C. doi:10.1098/rsta.2013.0376. PMC 3928907. PMID 24567480.

- ^ http://gow.epsrc.ac.uk/NGBOViewPerson.aspx?PersonId=5628 Grants awarded to Steve Furber by the Engineering and Physical Sciences Research Council

- ^ "Professor Stephen Furber CBE FREng FRS". London: Royal Society. Archived from the original on 17 November 2015.

- ^ BBC News: One of the designers of the classic BBC Micro computer has been recognised in the New Year Honours list

- ^ BBC Micro designer gets New Year's Honour ZDNet 2 January 2008

- ^ "Professor Stephen Furber: Creator of the ARM microprocessor". Millennium Prize. 9 June 2010. Retrieved 10 June 2010.

- ^ "Steve Furber". Computer History Museum. Retrieved 23 May 2013.

- ^ Williams, Alun (20 January 2012). "Four ARM cores for every person on earth – Furber, Wilson honoured". Electronics Weekly. Retrieved 7 March 2012.

- ^ Micro Men (TV 2009) at IMDb

External links

- Acorn recollections

- BBC News Technology – Home computing pioneer honoured 29 December 2007

- BBC News – Scientists to build 'brain box' 17 July 2006

- BBC News Technology – The Tech Lab: Steve Furber

- Lecture by Furber on the Future of Computer Technology

- Steve Furber Video Interview – 17-08-2009

- Steve Furber Talk @ Acorn World – 13-09-2009

- 1953 births

- Living people

- Acorn Computers

- ARM people

- English electrical engineers

- British computer scientists

- Computer designers

- School of Computer Science, University of Manchester

- Fellows of the Royal Society

- Fellows of the British Computer Society

- Fellows of the Royal Academy of Engineering

- Fellow Members of the IEEE

- Alumni of Emmanuel College, Cambridge

- Alumni of St John's College, Cambridge

- Academics of the University of Manchester

- People from Manchester

- People educated at Manchester Grammar School

- Commanders of the Order of the British Empire

- Fellows of the Institution of Engineering and Technology

- International Mathematical Olympiad participants