Delta-sigma modulation: Difference between revisions

Puffingbilly (talk | contribs) |

|||

| Line 13: | Line 13: | ||

* The whole structure is simpler, only one integrator is needed, and the demodulator can be a simple RC filter to reconstruct the signal |

* The whole structure is simpler, only one integrator is needed, and the demodulator can be a simple RC filter to reconstruct the signal |

||

* The quantized value is the integral of the difference signal, which makes it less sensitive to the rate of change of the signal. |

* The quantized value is the integral of the difference signal, which makes it less sensitive to the rate of change of the signal. |

||

****************************** |

|||

Note added by another author:- |

|||

The method can be thought of as a voltage controlled oscillator, where the controlling voltage is the voltage to be measured and where linearity and proportionality is determined by a negative feedback loop. |

|||

The output of the oscillator is a pulse stream, each pulse of which is a known, constant, amplitude and duration but variable separating interval. The interval between pulses is determined by the feedback loop so that a low input voltage produces a long interval between pulses and a high input voltage produces a short interval between pulses. |

|||

Counting the pulses produced in the way described above in a fixed summing interval produces a count proportional to the input voltage to be measured. |

|||

Variations in scaling can be produced by either varying the fixed summing interval or by counting down the pulses by a fixed ratio or both methods can be used. |

|||

The output count finally produced is the digitization of the input voltage. |

|||

18:45, 26 July 2007 (UTC)18:45, 26 July 2007 (UTC)18:45, 26 July 2007 (UTC)~p |

|||

== Principle == |

== Principle == |

||

Revision as of 18:45, 26 July 2007

The Delta-Sigma (ΔΣ) modulation is a kind of analog-to-digital or digital-to-analog conversion. An analog to digital converter (ADC) or DAC circuit which implements this technique can be easily realized using low-cost CMOS processes, such as the processes used to produce digital integrated circuits; for this reason, even though it was first presented in the early 1960s, it is only in recent years that it has come into widespread use with improvements in silicon technology. Almost all analog integrated circuit vendors offer sigma delta converters.

Derivation from Δ-modulation

ΔΣ modulation is derived from another kind of conversion known as delta modulation. In Fig.2, is shown, in a simplified way, how this derivation is done:

- Start with a block diagram of a Δ-modulator/demodulator.

- The linearity property of the integral operation () makes it possible to move the integrator, which reconstructs the analog signal in the demodulator section, in front of the Δ-modulator.

- Again, the linearity property of the integral operation allows the two integrators to be combined and a ΔΣ-modulator/demodulator block diagram is obtained.

The spectrum shaping of the two types of modulation is different: ΔΣ-modulation shapes the noise, leaving the signal as it is, while Δ-modulation shapes both noise and signal equally.

In general, ΔΣ has some advantages versus Δ modulation:

- The whole structure is simpler, only one integrator is needed, and the demodulator can be a simple RC filter to reconstruct the signal

- The quantized value is the integral of the difference signal, which makes it less sensitive to the rate of change of the signal.

Note added by another author:-

The method can be thought of as a voltage controlled oscillator, where the controlling voltage is the voltage to be measured and where linearity and proportionality is determined by a negative feedback loop. The output of the oscillator is a pulse stream, each pulse of which is a known, constant, amplitude and duration but variable separating interval. The interval between pulses is determined by the feedback loop so that a low input voltage produces a long interval between pulses and a high input voltage produces a short interval between pulses. Counting the pulses produced in the way described above in a fixed summing interval produces a count proportional to the input voltage to be measured. Variations in scaling can be produced by either varying the fixed summing interval or by counting down the pulses by a fixed ratio or both methods can be used. The output count finally produced is the digitization of the input voltage. 18:45, 26 July 2007 (UTC)18:45, 26 July 2007 (UTC)18:45, 26 July 2007 (UTC)~p

Principle

The principle of the ΔΣ architecture is to make rough evaluations of the signal, to measure the error, integrate it and then compensate for that error. The mean output value is then equal to the mean input value if the integral of the error is finite. A demonstration applet is available online to simulate the whole architecture. [1]

The number of integrators, and consequently, the numbers of feedback loops, indicates the order of a ΔΣ-modulator; a 2nd order ΔΣ modulator is shown in Fig. 3. First order modulators are stable, but for higher order ones stability must be taken into great account.

The modulator can also be classified by the number of bits it has in output, which strictly depends on the output of the quantizer. The quantizer can be realized with a N-level comparator, thus the modulator has log2N-bit output; for instance, a 1-bit modulator has a quantizer realized as a simple 2-level comparator (a comparator referred to 0), whose output is 1 or 0 if the input signal is positive or negative.

Quantization theory formulas

When a signal is quantized, the resulting signal approximately has the second-order statistics of a signal with independent additive white noise. Assuming that the signal value is in the range of one step of the quantized value with an equal distribution, the root mean square value of this quantization noise is

In reality, the quantization noise is of course not independent of the signal; this dependence is the source of idle tones and pattern noise in Sigma-Delta converters.

Oversampling ratio, where is the sampling frequency and is Nyquist rate

The rms noise voltage within the band of interest can be expressed in terms of OSR

Structures

The MASH (Multi-stAge noise SHaping) structure has a noise shaping property, and is commonly used in digital audio and fractional-N frequency synthesizers. It comprises two or more cascaded overflowing accumulators, each of which is equivalent to a first-order sigma delta modulator. The carry outputs are combined through summations and delays to produce a binary output, the width of which depends on the number of stages (order) of the MASH. Besides its noise shaping function, it has two more attractive properties:

- simple to implement in hardware; only common digital blocks such as accumulators, adders, and D flip-flops are required

- unconditionally stable (there are no feedback loops outside the accumulators)

Oversampling

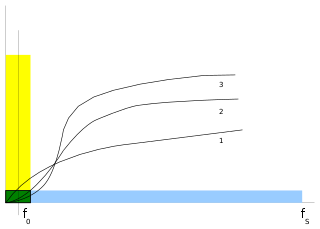

Let's consider a signal at frequency and a sampling frequency of much higher than Nyquist rate (see Fig. 4). ΔΣ modulation is based on the technique of oversampling to reduce the noise in the band of interest (green), which also avoids the use of high-precision analog circuits for the anti-aliasing filter. The quantization noise is the same both in a Nyquist converter (in yellow) and in an oversampling convertor (in blue), but it is distributed over a larger spectrum. In ΔΣ-converters, noise is further reduced at low frequencies, which is the band where the signal of interest is, and it is increased at the higher frequencies, where it can be filtered. This property is known as noise shaping.

For a first order delta sigma modulator, the noise is shaped by a filter with transfer function . Assuming that the sampling frequency , the quantization noise in the desired signal bandwidth can be approximated as:

.

Similarly for a second order delta sigma modulator, the noise is shaped by a filter with transfer function . The in-band quantization noise can be approximated as:

.

In general, for a -order ΔΣ-modulator, the variance of the in-band quantization noise:

.

When the sampling frequency is doubled, the signal to quantization noise is improved by for a -order ΔΣ-modulator. Higher the oversampling ratio, the higher the signal-to-noise ratio and the higher the resolution in bits.

Another key aspect given by oversampling is the speed/resolution tradeoff. In fact, the decimation filter put after the modulator not only filters the whole sampled signal in the band of interest (cutting the noise at higher frequencies), but also reduces the frequency of the signal increasing its resolution. This is obtained by a sort of averaging of the higher data rate bitstream.

Example of decimation

Let's have, for instance, an 8:1 decimation filter and a 1-bit bitstream; if we have an input stream like 10010110, counting the number of ones, the decimation result is 4/8 = 0.5 = 100 in binary; in other words,

- the sample frequency is reduced by a factor of eight

- the serial (1-bit) input bus becomes a parallel (3-bits) output bus.

Naming

As can be easily recognized from a previous section, the name Delta-Sigma comes directly from the presence of a Delta modulator and an integrator, as firstly introduced by Inose et al. in their patent application.[2] Very often, the name Sigma-Delta is used as a synonym, but nowadays IEEE publications mostly use Delta-Sigma.

Notes

- ^ Analog Devices : Virtual Design Center : Interactive Design Tools : Sigma-Delta ADC Tutorial

- ^ H. Inose, Y. Yasuda, J. Murakami, "A Telemetering System by Code Manipulation -- ΔΣ Modulation," IRE Trans on Space Electronics and Telemetry, Sep. 1962, pp. 204-209.

See also

External links

- Sigma-delta techniques extend DAC resolution article by Tim Wescott 2004-06-23

- Tutorial on Designing Delta-Sigma Modulators: Part I (2004-03-30) and Part II (2004-04-01) a tutorial by Mingliang Liu

- Gabor Temes' Publications

- Bruce Wooley's Delta-Sigma Converter Projects

- An Introduction to Delta Sigma Converters (which covers both ADC's and DAC's sigma-delta)

- Demystifying Sigma-Delta ADCs. This in-depth article covers the theory behind a Delta-Sigma analog-to-digital converter.

- Motorola digital signal processors: Principles of sigma-delta modulation for analog-to-digital converters

- One-Bit Delta Sigma D/A Conversion Part I: Theory article by Randy Yates presented at the 2004 comp.dsp conference

- MASH (Multi-stAge noise SHaping) structure with both theory and a block-level implementation of a MASH

- How a Sigma-Delta ADC Works at TechOnline free registration required to read the article

- Simple Sigma Delta Modulator example Contains Block-diagrams, code, and simple explanations

Bibliography

- R.J. Baker. CMOS Mixed-Signal Circuit Design. ISBN 0-47122-754-0.

{{cite book}}: Check|isbn=value: checksum (help) - J. Candy, G. Temes. Oversampling Delta-sigma Data Converters. ISBN 0-87942-285-8.

- S. Norsworthy, R. Schreier, G. Temes. Delta-Sigma Data Converters. ISBN 0-7803-1045-4.

{{cite book}}: CS1 maint: multiple names: authors list (link) - Mingliang Liu. Demystifying Switched-Capacitor Circuits. ISBN 0-7506-7907-7.

- R. Schreier, G. Temes. Understanding Delta-Sigma Data Converters. ISBN 0-471-46585-2.

- V. Peluso, M. Steyaert, W. Sansen. Design of Low-Voltage Low-Power CMOS Delta-Sigma A/D Converters. ISBN 0-7923-8417-7.

{{cite book}}: Check|isbn=value: checksum (help)CS1 maint: multiple names: authors list (link)

![{\displaystyle H_{n}(z)=\left[1-z^{-1}\right]}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a11ad41b39c5fc1c3e8f315b47bc87a72c7fab1c)

![{\displaystyle H_{n}(z)=\left[1-z^{-1}\right]^{2}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/a80d70b2839882e5d0bbd76fa9ee64da017d12d9)