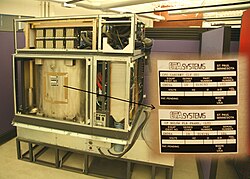

ETA10

An ETA10 displayed at the Computer History Museum | |

| Also known as | Cyber 2XX, GF-10 |

|---|---|

| Developer | ETA Systems |

| Manufacturer | ETA Systems |

| Type | Vector supercomputer |

| Release date | December 1986 |

| Operating system | EOS, UNIX System V (Release 3) |

| Predecessor | CDC Cyber 205 |

The ETA10 is a vector supercomputer designed, manufactured, and marketed by ETA Systems, a spin-off division of Control Data Corporation (CDC). The ETA10 was an evolution of the CDC Cyber 205, which can trace its origins back to the CDC STAR-100, one of the first vector supercomputers to be developed.[1][Note 1]

CDC announced it was creating ETA Systems, and a successor to the Cyber 205, on 18 April 1983 at the Frontiers of Supercomputing conference, held at the Los Alamos National Laboratory.[2] It was then referred to tentatively as the Cyber 2XX, and later as the GF-10, before it was named the ETA10.[3] Prototypes were operational in mid-1986, and the first delivery was made in December 1986. The supercomputer was formally announced in April 1987 at an event held at its first customer installation, the Florida State University, Tallahassee's Scientific Computational Research Institute.[4] On 17 April 1989, CDC abruptly closed ETA Systems due to ongoing financial losses, and discontinued production of the ETA10.[5] Many of its users, such as Florida State University, negotiated Cray hardware in exchange.[6]

Historical development

CDC had a strong history of creating powerful supercomputers, starting with the CDC 6600. One of the most famous computer architects to emerge from CDC was Seymour Cray. After a disagreement with CDC management regarding the development of the CDC 8600, he went on to form his own supercomputer company, Cray Research. Meanwhile, work continued at CDC in developing a high-end supercomputer, the CDC STAR-100—led by another famous architect, Neil Lincoln. Cray Research's Cray-1 vector supercomputer was successful, beating CDC's STAR-100. CDC responded with derivatives of the STAR, the Cyber 203 and 205. The Cyber 205 was moderately successful against the Cray-1's successor, the Cray X-MP. It became apparent to CDC's top management that it needed to decrease the development time for the next generation computer—thus a new approach was considered for the follow-on to the Cyber 205.

After spinning off from CDC in September 1983, ETA set a goal of producing a supercomputer with a cycle time less than 10ns. To accomplish this, several innovations were made. Among these was the use of liquid nitrogen for cooling the CMOS-based CPUs.

The ETA10 successfully met the company's initial goals (10 GFLOPS), with some models achieving a cycle time of about 7 ns (143 MHz) - considered rapid by mid-1980s standards. They delivered seven liquid nitrogen-cooled versions and 27 smaller, air-cooled versions. The CMOS circuits produced only a fraction of the heat of previous ICs. The planned 1987 follow-on was supposed to be designated Cyber 250 or ETA30, as in 30 GFLOPS. ETA was eventually reincorporated back into CDC, ceasing operations on April 17, 1989.

Operating systems and applications

The ETA10 series could run either ETA's EOS operating system, which was widely criticized for various problems, or a port by Lachman Associates, a software personnel firm, of UNIX System V (Release 3). While EOS suffered a reputation for poor quality, ETA's UNIX was better received by customers.

EOS was preceded by and was binary executable compatible with the CDC VSOS operating system for Cyber 205. Like VSOS, EOS had demand paged virtual memory (the VS part) with 2 page sizes for improved virtual memory performance with the ETA's faster hardware pipelines. Though it had roots in the interactive Livermore Time Sharing System (LTSS), VSOS was focused as a batch-oriented operating system. VSOS was not run at very many institutions and its application-oriented performance, while the historic focus for supercomputing, set its features behind the times because of its limited user base.

To address this feature deficiency and to make the operating system more "normal to use", the VSOS characteristics were married with UNIX characteristics in a hybrid OS. The OS was intended to be effective for both batch work that drove the hardware to its maximum or for interactive use in development from a UNIX workstation.

EOS was written mainly in Cybil, a Pascal-like programming language created by Control Data for its later Cyber operating systems. It was a new effort, as VSOS was implemented in IMPL, a Fortran-like language created for the LTSS implementation. The command line appearance of all these systems was similar to the lineage going back to UNIVAC EXEC*8.

EOS was released with early hardware deliveries and had some of the typical problems for early OS releases. Some customers delayed payment for their supercomputer installations.

ETA later released a port of UNIX for the ETA-10 line, which was more quickly accepted by their customer base. However, this port started as a single-processor kernel which did not transparently exploit the hardware architecture with up to 8 large application CPUs for applications.

Criticism

Despite eventual adoption of UNIX, poorly developed system software remained one flaw of the ETA10 line. According to one description of the system:

- Without NSF funding, the von Neumann center could be doomed. "I don’t think we can function without federal support," says Cohen. Even if the center does operate at a vastly reduced level, its machines continue to be plagued by software problems. The NSF review panel found that the ETA10 suffered a software failure once every 30 hours, and that its ability to run programs on more than one of its eight processors at any one time was poor. Although its hardware is still considered state-of-the-art, the overall package is an "extremely immature computer system," the panel concluded.[7]

The late delivery and operating problems contributed to this demise as well as management problems.[8]

It is a mistake to believe that ETA's demise was based solely on operating system choice or existence. The Fortran compiler (ftn200) had not changed from the CDC205. This compiler retained vendor-specific programming performance features (known as the Q8* subroutine calls) in an era when supercomputer users were realizing the necessity of source code portability between architectures. Additionally, the compiler optimizations were not keeping up with existing technology as shown by the Japanese supercomputer vendors as well as the newer minisupercomputer makers and competition at Cray Research.

In general, computer hardware manufacturers prior and up to that period tended to be weak on software. Libraries and available commercial and non-commercial applications help build an installed user base. CDC was relatively weak in this area, and some of the best operating systems that CDC provided to customers were productized versions of an OS written by Lawrence Livermore Laboratories.

According to NASA, the hardware was very poorly designed, and failed to complete any acceptance tests at the Ames Research Center. This one event is considered among CDC insiders to be the downfall of ETA, which folded as a result of NASA saying no (and in a domino effect DOD, etc.).

Models

There were four models of the ETA10. Any of these models could be built in either single- or multi-processor configurations.

The Models E and G were the highest-performing members of the ETA10 line, and used liquid nitrogen cooling to achieve rapid cycle times. The first to be announced was the Model E, whose processors had a 10.5 ns clock cycle (approximately 95 MHz). The Model E could support up to eight processors, for a peak performance of 8.32 GFLOPS. The later Model G, whose processors had a 7 ns clock cycle (approximately 142 MHz), had a peak performance of 10.3 GFLOPS in its maximal eight-processor configuration.

The Models P and Q were slower, less-costly, air-cooled versions. The Model P, codenamed "Piper", had processors with a 24 ns clock cycle. The faster, two-processor Model Q had a 19 ns clock cycle.

Performance

Between the highest-performing, liquid-nitrogen cooled models (ETA10-E, G, etc.) and the cheaper, air-cooled models (ETA10-P, Q, etc.), the ETA10 line spanned a 27:1 performance range. Peak performance on the top-of-the-line models reached 10 GFLOPS.

A single-processor ETA10 achieved 52 MFLOPS on the LINPACK benchmark[9] for a matrix with a size of 100 × 100.

Description

The ETA10 was a multiprocessor system that supported up to eight CPUs. Each CPU was similar to that of a two-lane Cyber 205. One of the main innovations of the ETA10 was how the CPU was implemented: the CPU was made of 250 CMOS gate array integrated circuits mounted on a 44-layer printed circuit board (PCB). Each gate array contained 20,000 gates and was fabricated using 1.25-micrometre (μm) technology that was accessible from the VHSIC program at Honeywell. In contrast, mainstream commercial technology at the time was in the 3 to 5 μm range.[10][11]

CMOS circuitry, which was not typically used in vector supercomputer CPUs at the time, was chosen because of the high density achievable, which reduces both the on-chip and off-chip delay. The CPU delays were managed through careful tuning of each PCB manufactured in conjunction with the logic technology and incorporated two key technologies known as JTAG and BIST. The gate arrays were designed using a combination of internally developed simulator and placement tools, and one of the first commercial electronic design automation tools (an application for schematic capture) from Mentor Graphics. Prior to the use of schematic capture at ETA, designers used textual netlists to describe the interconnection of the logic circuits.

However, CMOS circuitry at that time was significantly slower than that of bipolar circuitry, especially the emitter-coupled logic that was widely used in vector supercomputer CPUs at the time. To compensate for this, the CPU was immersed in -196.15 °C liquid nitrogen for cooling. Although such cooling could potentially speed up the CMOS logic by a factor of four, in practice the liquid nitrogen cooling yielded an approximately twofold speed increase over air-cooled systems. However, because liquid nitrogen cooling yielded only marginal performance benefits, none of the ETA10 systems used such cooling for either the local or shared memories. It is of particular note that in order for this type of cooling to be effective, a closed-loop system was required. ETA had to innovate to make this possible, since there were not any commercially available solutions in the market. The 44-layer PCB was also innovative, and ETA had to develop new processes to manufacture it.

Each CPU had its own 4 million word local memory built from SRAM ICs. Each CPU is also connected to a 256 million word shared memory built from DRAM ICs. In addition to these memories, there is a communication buffer used for CPU synchronization and other multiprocessor-related protocol communication. I/O was facilitated by one to eighteen I/O processors that each have a direct path to the shared memory. The ETA10 used fiber-optic lines for communication between the CPUs and I/O devices, a novel approach for systems interconnection in the 1980s.

Installations

Before ETA Systems was reincorporated into CDC, a total of 25 systems were delivered. Among the recipients were:

- Florida State University (took delivery of the first ETA10 system, serial number 1, on January 5, 1987)

- Johnson Space Center

- John von Neumann Center (JVNC), (when no buyers could be found for the two ETA10 machines at this center, they were destroyed with sledgehammers to prevent illicit use)

- Purdue University (contributed to ETA System V, the System V UNIX variant that ran on the ETA10).

- Tokyo Institute of Technology Took delivery of an 8-CPU liquid-cooled system in 1988

- Meiji University Took delivery of an ETA10-P system in 1989

- Academia Sinica

- Deutscher Wetterdienst

By the end of the 1980s, the remaining ETA10 systems were donated to high schools through a computer science competition, SuperQuest:

See also

- EOS, the operating system ETA Systems developed in-house

- Cray Time Sharing System

- NLTSS

- Timeline of operating systems

Notes

- ^ The other vector supercomputer introduced at around the same time was the Texas Instruments Advanced Scientific Computer (ASC).

References

- ^ Ibbett, R.N.; Topham, N.P. (1989). Architecture of High Performance Computers, Volume I: Uniprocessors and vector processors. Springer-Verlag. p. 156.

- ^ Schrage, Michael (19 August 1983). "CDC Enters Supercomputer Race". The Washington Post.

- ^ Hockney, R.W. (June 1985). "MIMD Computing in the USA—1984". Parallel Computing. 2 (2): 119–136. doi:10.1016/0167-8191(85)90024-9.

- ^ Gibson, Stanley (4 May 1987). "Super-fast ETA computer debuts". Computerworld.

- ^ Markoff, John (18 April 1989). "Control Data Plans Shifts To End Slide". The New York Times.

- ^ Bauer, Jeff (1991), A History of Supercomputing at Florida State University

- ^ Anderson, Christopher (Nov 27, 1989), "NSF Supercomputer Program Looks Beyond Princeton Recall", The Scientist, vol. 3, no. 23, p. 2

- ^ Brenner, Al (1994), "The John von Neumann Computer Center: An Analysis", in Karyn R. Ames; Alan Brenner (eds.), Frontiers of Supercomputing II: A National Reassessment, pp. 469–480

- ^ Bozman, Jean S. (30 November 1987). "ETA called fastest super". Computerworld.

- ^ Trew, Arthur; Wilson, Greg (1991). Past, Parallel, Present: A Survey of Available Parallel Computer Systems. Springer-Verlag. pp. 323–329.

- ^ Hockney, R.W.; Jesshope, C.R. (1988). Parallel Computers: Architecture, Programming and Algorithms (2 ed.). Adam Hilger. pp. 185–190.

External links

- A description of computer systems at the Waalsdorp museum, including the ETA line

- Another page at Waalsdorp, including a block diagram of the ETA architecture

- IEEE article about the ETA10 liquid-nitrogen-cooled supercomputer system

- The ETA Saga

- A brief history of the hardware technology developed for the ETA Systems ETA-10