CDC 6600

| CDC 6600 | |

|---|---|

3D rendering with a figure as scale | |

| Design | |

| Manufacturer | Control Data Corporation |

| Designer | Seymour Cray |

| Release date | September 1964[1] |

| Units sold | 100+[2] |

| Price | $2,370,000[3] |

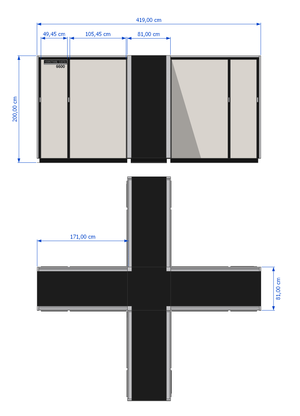

| Casing | |

| Dimensions | Height : 200 cm (79 in) Cabinet width: 89 cm (35 in)[4] Cabinet length : 183 cm (72 in)[4] |

| Weight | about 12,000 pounds (6.0 short tons; 5.4 t)[5] |

| Power | 30 kW @ 208 V 400 Hz[6][3] |

| System | |

| Operating system | SCOPE, KRONOS[7] |

| CPU | 60-bit processor @ 10 MHz[8] |

| Memory | Up to 982 kilobytes (131000 x 60 bits)[1] |

| MIPS | 2 MIPS[8] |

| Predecessor | CDC 1604 |

| Successor | CDC 7600 |

The CDC 6600 was the flagship of the 6000 series of mainframe computer systems manufactured by Control Data Corporation.[9][10] Generally considered to be the first successful supercomputer, it outperformed the industry's prior record holder, the IBM 7030 Stretch, by a factor of three.[11][12] With performance of up to three megaFLOPS,[13][14] the CDC 6600 was the world's fastest computer from 1964 to 1969, when it relinquished that status to its successor, the CDC 7600.[15]

The first CDC 6600s were delivered in 1965 to Livermore and Los Alamos.[16] They quickly became a must-have system in high-end scientific and mathematical computing, with systems being delivered to Courant Institute of Mathematical Sciences, CERN,[17] the Lawrence Radiation Laboratory,[18] and many others. At least 100 were delivered in total.[2]

A CDC 6600 is on display at the Computer History Museum in Mountain View, California. The only running CDC 6000 series machine has been restored by Living Computers: Museum + Labs.

History and impact

CDC's first products were based on the machines designed at ERA, which Seymour Cray had been asked to update after moving to CDC. After an experimental machine known as the Little Character,[19] in 1960 they delivered the CDC 1604, one of the first commercial transistor-based computers, and one of the fastest machines on the market. Management was delighted, and made plans for a new series of machines that were more tailored to business use; they would include instructions for character handling and record keeping for instance. Cray was not interested in such a project, and set himself the goal of producing a new machine that would be 50 times faster than the 1604. When asked to complete a detailed report on plans at one and five years into the future, he wrote back that his five-year goal was "to produce the largest computer in the world", "largest" at that time being synonymous with "fastest", and that his one-year plan was "to be one-fifth of the way".

Taking his core team to new offices nearby the original CDC headquarters, they started to experiment with higher quality versions of the "cheap" transistors Cray had used in the 1604. After much experimentation, they found that there was simply no way the germanium-based transistors could be run much faster than those used in the 1604. The "business machine" that management had originally wanted, now forming as the CDC 3000 series, pushed them about as far as they could go. Cray then decided the solution was to work with the then-new silicon-based transistors from Fairchild Semiconductor, which were just coming onto the market and offered dramatically improved switching performance.

During this period, CDC grew from a startup to a large company and Cray became increasingly frustrated with what he saw as ridiculous management requirements. Things became considerably more tense in 1962 when the new CDC 3600 started to near production quality, and appeared to be exactly what management wanted, when they wanted it. Cray eventually told CDC's CEO, William Norris that something had to change, or he would leave the company. Norris felt he was too important to lose, and gave Cray the green light to set up a new laboratory wherever he wanted.

After a short search, Cray decided to return to his home town of Chippewa Falls, Wisconsin, where he purchased a block of land and started up a new laboratory.

Although this process introduced a fairly lengthy delay in the design of his new machine, once in the new laboratory, without management interference, things started to progress quickly. By this time, the new transistors were becoming quite reliable, and modules built with them tended to work properly on the first try. The 6600 began to take form, with Cray working alongside Jim Thornton, system architect and "hidden genius" of the 6600.

More than 100 CDC 6600s were sold over the machine's lifetime. Many of these went to various nuclear weapon-related laboratories, and quite a few found their way into university computing laboratories. Cray immediately turned his attention to its replacement, this time setting a goal of ten times the performance of the 6600, delivered as the CDC 7600. The later CDC Cyber 70 and 170 computers were very similar to the CDC 6600 in overall design and were nearly completely backwards compatible.

The 6600 was three times faster than the previous record-holder, the IBM 7030 Stretch; this alarmed IBM. Then-CEO Thomas Watson Jr. wrote a memo to his employees: "Last week, Control Data ... announced the 6600 system. I understand that in the laboratory developing the system there are only 34 people including the janitor. Of these, 14 are engineers and 4 are programmers ... Contrasting this modest effort with our vast development activities, I fail to understand why we have lost our industry leadership position by letting someone else offer the world's most powerful computer." Cray's reply was sardonic: "It seems like Mr. Watson has answered his own question."[20][21]

Description

Typical machines of the era used a single CPU to drive the entire system.[22] A typical program would first load data into memory (often using pre-rolled library code), process it, and then write it back out. This required the CPUs to be fairly complex in order to handle the complete set of instructions they would be called on to perform. A complex CPU implied a large CPU, introducing signalling delays while information flowed between the individual modules making it up. These delays set a maximum upper limit on performance, as the machine could only operate at a cycle speed that allowed the signals time to arrive at the next module.

Cray took another approach. At the time, CPUs generally ran slower than the main memory to which they were attached. For instance, a processor might take 15 cycles to multiply two numbers, while each memory access took only one or two. This meant there was a significant time where the main memory was idle. It was this idle time that the 6600 exploited.

The CDC 6600 used a simplified core processor that was designed to run mathematical and logic operations as rapidly as possible, which demanded it be built as small as possible to reduce the length of wiring and the associated signalling delays. This led to the machine's (typically) cross-shaped main chassis with the circuit boards for the CPU arranged close to the center. Supporting the CPU were ten peripheral processors that handled input and output, as well as controlling what data was sent into the main CPU for processing. The 6600 used a 60-bit word and a ones' complement representation of integers, something that later CDC machines would use into the late 1980s, making them the last systems besides some DSPs to use this architecture.[23]

Instead of trying to make the CPU handle all the tasks, the 6600 CPUs handled arithmetic and logic only. This resulted in a much smaller CPU that could operate at a higher clock speed. Combined with the faster switching speeds of the silicon transistors, the new CPU design easily outperformed everything then available. The new design ran at 10 MHz (100 ns cycle), about ten times faster than other machines on the market. In addition to the clock being faster, the simple processor executed instructions in fewer clock cycles; for instance, the CPU could complete a multiplication in ten cycles.

Peripheral processors (characteristics)

However, the CPU could only execute a limited number of simple instructions. A typical CPU of the era had a complex instruction set, which included instructions to handle all the normal "housekeeping" tasks, such as memory access and input/output. Cray instead implemented these instructions in separate, simpler processors dedicated solely to these tasks, leaving the CPU with a much smaller instruction set. This was the first of what later came to be called reduced instruction set computer (RISC) design.

By allowing the CPU, peripheral processors (PPs) and I/O to operate in parallel, the design considerably improved the performance of the machine. Under normal conditions a machine with several processors would also cost a great deal more. Key to the 6600's design was to make the I/O processors, known as peripheral processors (PPs), as simple as possible. The PPs were based on the simple 12-bit CDC 160-A, which ran much slower than the CPU, gathering up data and transmitting it as bursts into main memory at high speed via dedicated hardware.

The 10 PPs were implemented virtually; there was CPU hardware only for a single PP.[24]: pp.4-3 thru 4-4 This CPU hardware was shared and operated on 10 PP register sets which represented each of the 10 PP states (similar to modern multithreading processors). The PP register barrel would "rotate", with each PP register set presented to the "slot" which the actual PP CPU occupied. The shared CPU would execute all or some portion of a PP's instruction whereupon the barrel would "rotate" again, presenting the next PP's register set (state). Multiple "rotations" of the barrel were needed to complete an instruction. A complete barrel "rotation" occurred in 1000 nanoseconds (100 nanoseconds per PP), and an instruction could take from one to five "rotations" of the barrel to be completed, or more if it was a data transfer instruction.

Instruction-set architecture

The basis for the 6600 CPU is what would today be called a RISC system, one in which the processor is tuned to do instructions which are comparatively simple and have limited and well-defined access to memory. The philosophy of many other machines was toward using instructions which were complicated — for example, a single instruction which would fetch an operand from memory and add it to a value in a register. In the 6600, loading the value from memory would require one instruction, and adding it would require a second one. While slower in theory due to the additional memory accesses, the fact that in well-scheduled code, multiple instructions could be processing in parallel offloaded this expense. This simplification also forced programmers to be very aware of their memory accesses, and therefore code deliberately to reduce them as much as possible.

Models

The CDC 6000 series included four basic models, the CDC 6400, the CDC 6500, the CDC 6600, and the CDC 6700. The models of the 6000 series differed only in their CPUs, which were of two kinds, the 6400 CPU and the 6600 CPU. The 6400 CPU had a unified arithmetic unit, rather than discrete functional units. As such, it could not overlap instructions' execution times. For example, in a 6400 CPU, if an add instruction immediately followed a multiply instruction, the add instruction could not be started till the multiply instruction finished, so the net execution time of the two instructions would be the sum of their individual execution times. The 6600 CPU had multiple functional units which could operate simultaneously, i.e., "in parallel", allowing the CPU to overlap instructions' execution times. For example, a 6600 CPU could begin executing an add instruction in the next CPU cycle following the beginning of a multiply instruction (assuming, of course, that the result of the multiply instruction was not an operand of the add instruction), so the net execution time of the two instructions would simply be the (longer) execution time of the multiply instruction. The 6600 CPU also had an instruction stack, a kind of instruction cache, which helped increase CPU throughput by reducing the amount of CPU idle time caused by waiting for memory to respond to instruction fetch requests. The two kinds of CPUs were instruction compatible, so that a program that ran on either of the kinds of CPUs would run the same way on the other kind but would run faster on the 6600 CPU. Indeed, all models of the 6000 series were fully inter-compatible. The CDC 6400 had one CPU (a 6400 CPU), the CDC 6500 had two CPUs (both 6400 CPUs), the CDC 6600 had one CPU (a 6600 CPU), and the CDC 6700 had two CPUs (one 6600 CPU and one 6400 CPU).

Central Processor (CP)

| CDC 6x00 registers | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

The Central Processor (CP) and main memory of the 6400, 6500, and 6600 machines had a 60-bit word length. The Central Processor had eight general purpose 60-bit registers X0 through X7, eight 18-bit address registers A0 through A7, and eight 18-bit "increment" registers B0 through B7. B0 was held at zero permanently by the hardware. Many programmers found it useful to set B1 to 1, and similarly treat it as inviolate.

The CP had no instructions for input and output, which are accomplished through Peripheral Processors (below). No opcodes were specifically dedicated to loading or storing memory; this occurred as a side effect of assignment to certain A registers. Setting A1 through A5 loaded the word at that address into X1 through X5 respectively; setting A6 or A7 stored a word from X6 or X7. No side effects were associated with A0. A separate hardware load/store unit, called the stunt box, handled the actual data movement independently of the operation of the instruction stream, allowing other operations to complete while memory was being accessed, which required eight cycles, in the best case.

The 6600 CP included ten parallel functional units, allowing multiple instructions to be worked on at the same time. Today, this is known as a superscalar processor design, but it was unique for its time. Unlike most modern CPU designs, functional units were not pipelined; the functional unit would become busy when an instruction was "issued" to it and would remain busy for the entire time required to execute that instruction. (By contrast, the CDC 7600 introduced pipelining into its functional units.) In the best case, an instruction could be issued to a functional unit every 100 ns clock cycle. The system read and decoded instructions from memory as fast as possible, generally faster than they could be completed, and fed them off to the units for processing. The units were:

- floating point multiply (two copies)

- floating point divide

- floating point add

- "long" integer add

- incrementers (two copies; performed memory load/store)

- shift

- boolean logic

- branch

Floating-point operations were given pride of place in this architecture: the CDC 6600 (and kin) stand virtually alone in being able to execute a 60-bit floating point multiplication in time comparable to that for a program branch.

Fixed point addition and subtraction of 60-bit numbers were handled in the Long Add Unit, using ones' complement for negative numbers. Fixed point multiply was done as a special case in the floating-point multiply unit—if the exponent was zero, the FP unit would do a single-precision 48-bit floating-point multiply and clear the high exponent part, resulting in a 48-bit integer result. Integer divide was performed by a macro, converting to and from floating point.[25]

Previously executed instructions were saved in an eight-word cache, called the "stack". In-stack jumps were quicker than out-of-stack jumps because no memory fetch was required. The stack was flushed by an unconditional jump instruction, so unconditional jumps at the ends of loops were conventionally written as conditional jumps that would always succeed.

The system used a 10 MHz clock, with a four-phase signal. A floating-point multiplication took ten cycles, a division took 29, and the overall performance, taking into account memory delays and other issues, was about 3 MFLOPS. Using the best available compilers, late in the machine's history, FORTRAN programs could expect to maintain about 0.5 MFLOPS.

Memory organization

User programs are restricted to use only a contiguous area of main memory. The portion of memory to which an executing program has access is controlled by the RA (Relative Address) and FL (Field Length) registers which are not accessible to the user program. When a user program tries to read or write a word in central memory at address a, the processor will first verify that a is between 0 and FL-1. If it is, the processor accesses the word in central memory at address RA+a. This process is known as base-bound relocation; each user program sees core memory as a contiguous block words with length FL, starting with address 0; in fact the program may be anywhere in the physical memory. Using this technique, each user program can be moved ("relocated") in main memory by the operating system, as long as the RA register reflects its position in memory. A user program which attempts to access memory outside the allowed range (that is, with an address which is not less than FL) will trigger an interrupt, and will be terminated by the operating system. When this happens, the operating system may create a core dump which records the contents of the program's memory and registers in a file, allowing the developer of the program a means to know what happened. Note the distinction with virtual memory systems; in this case, the entirety of a process's addressable space must be in core memory, must be contiguous, and its size cannot be larger than the real memory capacity.

All but the first seven CDC 6000 series machines could be configured with an optional Extended Core Storage (ECS) system. ECS was built from a different variety of core memory than was used in the central memory. This made it economical for it to be both larger and slower. The primary reason was that ECS memory was wired with only two wires per core (contrast with five for central memory). Because it performed very wide transfers, its sequential transfer rate was the same as that of the small core memory. A 6000 CPU could directly perform block memory transfers between a user's program (or operating system) and the ECS unit. Wide data paths were used, so this was a very fast operation. Memory bounds were maintained in a similar manner as central memory, with an RA/FL mechanism maintained by the operating system. ECS could be used for a variety of purposes, including containing user data arrays that were too large for central memory, holding often-used files, swapping, and even as a communication path in a multi-mainframe complex.

Peripheral Processors (PPs)

To handle the "housekeeping" tasks, which in other designs, were assigned to the CPU, Cray included ten other processors, based partly on his earlier computer, the CDC 160-A. These machines, called Peripheral Processors, or PPs, were full computers in their own right, but were tuned to performing I/O tasks and running the operating system. (Substantial parts of the operating system ran on the PPs; thus leaving most of the power of the Central Processor available for user programs.) Only the PPs had access to the I/O channels. One of the PPs was in overall control of the machine, including control of the program running on the main CPU, while the others would be dedicated to various I/O tasks. When the CP program needed to perform an operating system function, it would put a request in a known location (Reference Address + 1) monitored[26] by PP 0. If necessary, PP 0 would assign another PP to load any necessary code and to handle the request. The PP would then clear RA+1 to inform the CP program that the task was complete.

The unique role of PP0 in controlling the machine was a potential single point of failure, in that a malfunction here could shut down the whole machine, even if the nine other PPs and the CPU were still functioning properly. Cray fixed this in the design of the successor 7600, when any of the PPs could be the controller, and the CPU could reassign any one to this role.

Each PP included its own memory of 4096 12-bit words. This memory served for both for I/O buffering and program storage, but the execution units were shared by ten PPs, in a configuration called the Barrel and slot. This meant that the execution units (the "slot") would execute one instruction cycle from the first PP, then one instruction cycle from the second PP, etc. in a round robin fashion. This was done both to reduce costs, and because access to CP memory required 10 PP clock cycles: when a PP accesses CP memory, the data is available next time the PP receives its slot time.

Wordlengths, characters

The central processor had 60-bit words, while the peripheral processors had 12-bit words. CDC used the term "byte" to refer to 12-bit entities used by peripheral processors; characters were 6-bit, and central processor instructions were either 15 bits, or 30 bits with a signed 18-bit address field, the latter allowing for a directly addressable memory space of 128K words of central memory (converted to modern terms, with 8-bit bytes, this is 0.94 MB). The signed nature of the address registers limited an individual program to 128K words. (Later CDC 6000-compatible machines could have 256K or more words of central memory, budget permitting, but individual user programs were still limited to 128K words of CM.) Central processor instructions started on a word boundary when they were the target of a jump statement or subroutine return jump instruction, so no-operations were sometimes required to fill out the last 15, 30 or 45 bits of a word. Experienced assembler programmers could fine-tune their programs by filling these no-op spaces with misc instructions that would be needed later in the program.

The 6-bit characters, in an encoding called CDC display code,[27][28][29] could be used to store up to 10 characters in a word. They permitted a character set of 64 characters, which is enough for all upper case letters, digits, and some punctuation. It was certainly enough to write FORTRAN, or print financial or scientific reports. There were actually two variations of the CDC display code character sets in use — 64-character and 63-character. The 64-character set had the disadvantage that two consecutive ":" (colon) characters might be interpreted as the end of a line if they fell at the end of a 10-byte word. A later variant, called 6/12 display code, was also used in the Kronos and NOS timesharing systems to allow full use of the ASCII character set in a manner somewhat compatible with older software.[30]

With no byte addressing instructions at all, code had to be written to pack and shift characters into words. The very large words, and comparatively small amount of memory, meant that programmers would frequently economize on memory by packing data into words at the bit level.

Due to the large word size, and with 10 characters per word, it was often faster to process wordfuls of characters at a time, rather than unpacking/processing/repacking them. For example, the CDC COBOL compiler was actually quite good at processing decimal fields using this technique. These sorts of techniques are now commonly used in the "multi-media" instructions of current processors.

Physical design

The machine was built in a plus-sign-shaped cabinet with a pump and heat exchanger in the outermost 18 in (46 cm) of each of the four arms. Cooling was done with Freon circulating within the machine and exchanging heat to an external chilled water supply. Each arm could hold four chassis, each about 8 in (20 cm) thick, hinged near the center, and opening a bit like a book. The intersection of the "plus" was filled with cables that interconnected the chassis. The chassis were numbered from 1 (containing all 10 PPUs and their memories, as well as the 12 rather minimal I/O channels) to 16. The main memory for the CPU was spread over many of the chassis. In a system with only 64K words of main memory, one of the arms of the "plus" was omitted.

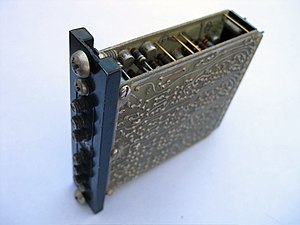

The logic of the machine was packaged into modules about 2.5 in (64 mm) square and about 1 in (2.5 cm) thick. Each module had a connector (30 pins, two vertical rows of 15) on one edge, and six test points on the opposite edge. The module was placed between two aluminum cold plates to remove heat. The module consisted of two parallel printed circuit boards, with components mounted either on one of the boards or between the two boards. This provided a very dense package; generally impossible to repair, but with good heat transfer characteristics. It was known as cordwood construction.

Operating system and programming

There was a sore point with the 6600 operating system support — slipping timelines. The machines originally ran a very simple job-control system known as COS (Chippewa Operating System), which was quickly "thrown together" based on the earlier CDC 3000 operating system in order to have something running to test the systems for delivery. However the machines were intended to be delivered with a much more powerful system known as SIPROS (for Simultaneous Processing Operating System), which was being developed at the company's System Sciences Division in Los Angeles. Customers were impressed with SIPROS' feature list, and many had SIPROS written into their delivery contracts.

SIPROS turned out to be a major fiasco. Development timelines continued to slip, costing CDC major amounts of profit in the form of delivery delay penalties. After several months of waiting with the machines ready to be shipped, the project was eventually cancelled. The programmers who had worked on COS had little faith in SIPROS and had continued working on improving COS.

Operating system development then split into two camps. The CDC-sanctioned evolution of COS was undertaken at the Sunnyvale, California software development laboratory. Many customers eventually took delivery of their systems with this software, then known as SCOPE (Supervisory Control Of Program Execution). SCOPE version 1 was, essentially, dis-assembled COS; SCOPE version 2 included new device and file system support; SCOPE version 3 included permanent file support, EI/200 remote batch support, and INTERCOM time-sharing support. SCOPE always had significant reliability and maintainability issues.

The underground evolution of COS took place at the Arden Hills, Minnesota assembly plant. MACE ([Greg] Mansfield And [Dave] Cahlander Executive) was written largely by a single programmer in the off-hours when machines were available. Its feature set was essentially the same as COS and SCOPE 1. It retained the earlier COS file system, but made significant advances in code modularity to improve system reliability and adaptiveness to new storage devices. MACE was never an official product, although many customers were able to wrangle a copy from CDC.

The unofficial MACE software was later chosen over the official SCOPE product as the basis of the next CDC operating system, Kronos, named after the Greek god of time. The story goes that Dave Mansfield called the University of Minnesota library and asked for an ancient word meaning "time". He wrote down "Kronos" instead of "Chronos". The main marketing reason for its adoption was the development of its TELEX time-sharing feature and its BATCHIO remote batch feature. Kronos continued to use the COS/SCOPE 1 file system with the addition of a permanent file feature.

An attempt to unify the SCOPE and Kronos operating system products produced NOS, (Network Operating System). NOS was intended to be the sole operating system for all CDC machines, a fact CDC promoted heavily. Many SCOPE customers remained software-dependent on the SCOPE architecture, so CDC simply renamed it NOS/BE (Batch Environment), and were able to claim that everyone was thus running NOS. In practice, it was far easier to modify the Kronos code base to add SCOPE features than the reverse.

The assembly plant environment also produced other operating systems which were never intended for customer use. These included the engineering tools SMM for hardware testing, and KALEIDOSCOPE, for software smoke testing. Another commonly used tool for CDC Field Engineers during testing was MALET (Maintenance Application Language for Equipment Testing), which was used to stress test components and devices after repairs or servicing by engineers. Testing conditions often used hard disk packs and magnetic tapes which were deliberately marked with errors to determine if the errors would be detected by MALET and the engineer.

The names SCOPE and COMPASS were used by CDC for both the CDC 6000 series, including the 6600, and the CDC 3000 series:

- The name COMPASS was used by CDC for the Assembly languages on both families.[32][33]

- The name SCOPE was used for its implementations on the 3000 and 6000 series.[34]

CDC 7600

The CDC 7600 was originally intended to be fully compatible with the existing 6000-series machines as well, it started life known as the CDC 6800. But during its design, the designers determined that maintaining complete compatibility with the existing 6000-series machines would limit how much performance improvement they could attain and decided to sacrifice compatibility for performance. While the CDC 7600's CPU was basically instruction compatible with the 6400 and 6600 CPUs, allowing code portability at the high-level language source code level, the CDC 7600's hardware, especially that of its Peripheral Processor Units (PPUs), was quite different, and the CDC 7600 required a different operating system. This turned out to be somewhat serendipitous because it allowed the designers to improve on some of the characteristics of the 6000-series design, such as the latter's complete dependence on Peripheral Processors (PPs), particularly the first (called PP0), to control operation of the entire computer system, including the CPU(s). Unlike the 6600 CPU, the CDC 7600's CPU could control its own operation. In fact, the 6000-series machines were retrofitted with this capability.

See also

Notes

- ^ a b Adams Survey 1968

- ^ a b "Control Data 6600: The Supercomputer Arrives". Archived from the original on 4 January 2001.

{{cite web}}:|archive-date=/|archive-url=timestamp mismatch; 7 July 2019 suggested (help) - ^ a b The Computer Directory And Buyer's Guide 1967

- ^ a b c Systems Hardware Handbook, Aug 75

- ^ "Control Data 6600: The Supercomputer Arrives". Dr. Dobb's. Archived from the original on 2017-06-05. Retrieved 2018-10-06.

- ^ CDC 6400 Central Processor Training Manual, Feb 67

- ^ Cyber 70 Product Announcement

- ^ a b Whetstone Benchmark History and Results

- ^ Cayton, Andrew R. L.; Sisson, Richard; Zacher, Chris (2006). The American Midwest: An Interpretive Encyclopedia. ISBN 0253003490.

- ^ "CDC 6600 – Historical Interlude: From the Mainframe to the Minicomputer Part 2, IBM and the Seven Dwarfs – They Create Worlds". November 8, 2014.

- ^ "Designed by Seymour Cray, the CDC 6600 was almost three times faster than the next fastest machine of its day, the IBM 7030 Stretch." Making a World of Difference: Engineering Ideas into Reality. National Academy of Engineering. 2014. ISBN 0309312655.

- ^ "In 1964 Cray's CDC 6600 replaced Stretch as the fastest computer on Earth." Sofroniou, Andreas (2013). Expert Systems, Knowledge Engineering for Human Replication. ISBN 1291595090.

- ^ Anthony, Sebastian (April 10, 2012). "The History of Supercomputers". ExtremeTech. Retrieved 2015-02-02.

- ^ "CDC 6600". Encyclopædia Britannica. Retrieved 2015-02-02.

- ^ "The 7600 design lasted longer than any other supercomputer design. It had the highest performance of any computer from its introduction in 1969 till the introduction of the Cray 1 in 1976." "CDC 7600".

- ^ N. Lewis, "Purchasing Power: Rivalry, Dissent, and Computing Strategy in Supercomputer Selection at Los Alamos," in IEEE Annals of the History of Computing, vol. 39 no. 3 (2017): 25-40, 2017 [1]

- ^ "The CDC 6600 arrives at CERN". CERN Timelines.

- ^ "Bumper Crop". Research Review. Lawrence Berkeley Laboratory. 1981.

- ^ "Control Data Corporation, "Little Character" Prototype". Computer History Museum. Retrieved 21 April 2016.

- ^ Mark D. Hill; Norman P. Jouppi; Gurindar S. Sohi, eds. (September 23, 1999). Readings in Computer Architecture. Morgan Kaufmann. p. 11. ISBN 978-1558605398.

- ^ An exact image of the memo appears in: "Watson Jr. memo about CDC 6600". August 28, 1963.

- ^ Smotherman, Mark; Spicer, Dag. "IBM's Single-Processor Supercomputer Efforts".

- ^ The UNIVAC 1100/2200 series still provides a ones'-complement environment, but using twos complement hardware.

- ^ Control Data 6000 Series Hardware Reference Manual (PDF). 1978.

- ^ "Archived copy". Archived from the original on 2014-01-02. Retrieved 2005-06-13.

{{cite web}}: CS1 maint: archived copy as title (link) - ^ This description covers early versions of CDC software; later versions used the Central Exchange jump (XJ) instruction to reduce the overhead for functions that could be performed entirely in the CP.

- ^ The term "Display code" was associated with CDC much as "EBCDIC" was *originally* associated with IBM. Other terms used in the industry were BCD and SIXBIT (the latter being preferred by DEC)

- ^ "DEC/PDP Character Codes".

- ^ "SIXBIT Character Code Reference". Archived from the original on 2016-11-24. Retrieved 2017-10-15.

- ^ "CDC Kronos" (PDF).

- ^ Understanding Computers: Speed and Power 1990, p. 17.

- ^ "COMPASS for 24 bit machines" (PDF). Archived from the original (PDF) on 2012-09-10. Retrieved 2017-10-15.

- ^ "COMPASS for 48 bit machines" (PDF).

- ^ "CDC delivered an early version of their SCOPE operating system for the 3600" Henley, Ernest J.; Lewins, Jeffery (2014). Advances in Nuclear Science and Technology. ISBN 1483215660.

References

- Grishman, Ralph (1974). Assembly Language Programming for the Control Data 6000 Series and the Cyber 70 Series. New York, NY: Algorithmics Press. [2]

- Control Data 6400/6500/6600 Computer Systems Reference Manual

- Thornton, J. (1963). Considerations in Computer Design – Leading up to the Control Data 6600 [3]

- Thornton, J. (1970). Design of a Computer—The Control Data 6600. Glenview, IL: Scott, Foresman and Co. [4]

- (1990) Understanding Computers: Speed and Power, a Time Life series ISBN 0809475863

External links

- Neil R. Lincoln with 18 Control Data Corporation (CDC) engineers on computer architecture and design, Charles Babbage Institute, University of Minnesota. Engineers include Robert Moe, Wayne Specker, Dennis Grinna, Tom Rowan, Maurice Hutson, Curt Alexander, Don Pagelkopf, Maris Bergmanis, Dolan Toth, Chuck Hawley, Larry Krueger, Mike Pavlov, Dave Resnick, Howard Krohn, Bill Bhend, Kent Steiner, Raymon Kort, and Neil R. Lincoln. Discussion topics include CDC 1604, CDC 6600, CDC 7600, CDC 8600, CDC STAR-100 and Seymour Cray.

- Parallel operation in the Control Data 6600, James Thornton

- Presentation of the CDC 6600 and other machines designed by Seymour Cray – by C. Gordon Bell of Microsoft Research (formerly of DEC)

- "CDC 6600's Five Year Reign". Computer History Museum. 2003.

The 6600 had 400,000 transistors and more than 100 miles of wiring.

– overview with pictures