Wafer fabrication

This article needs additional citations for verification. (September 2014) |

Wafer fabrication is a procedure composed of many repeated sequential processes to produce complete electrical or photonic circuits on semiconductor wafers in semiconductor device fabrication process. Examples include production of radio frequency (RF) amplifiers, LEDs, optical computer components, and microprocessors for computers. Wafer fabrication is used to build components with the necessary electrical structures.

The main process begins with electrical engineers designing the circuit and defining its functions, and specifying the signals, inputs/outputs and voltages needed. These electrical circuit specifications are entered into electrical circuit design software, such as SPICE, and then imported into circuit layout programs, which are similar to ones used for computer aided design. This is necessary for the layers to be defined for photomask production. The resolution of the circuits increases rapidly with each step in design, as the scale of the circuits at the start of the design process is already being measured in fractions of micrometers. Each step thus increases circuit density for a given area.

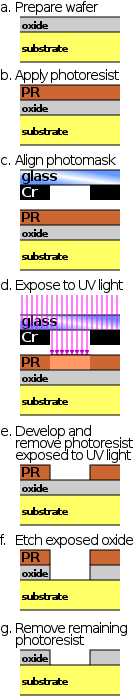

The silicon wafers start out blank and pure. The circuits are built in layers in clean rooms. First, photoresist patterns are photo-masked in micrometer detail onto the wafers' surface. The wafers are then exposed to short-wave ultraviolet light and the unexposed areas are thus etched away and cleaned. Hot chemical vapors are deposited on to the desired zones and baked in high heat, which permeate the vapors into the desired zones. In some cases, ions, such as O2+ or O+, are implanted in precise patterns and at a specific depth by using RF-driven ion sources.

These steps are often repeated many hundreds of times, depending on the complexity of the desired circuit and its connections.

New processes to accomplish each of these steps with better resolution and in improved ways emerge every year, with the result of constantly changing technology in the wafer fabrication industry. New technologies result in denser packing of minuscule surface features such as transistors and micro-electro-mechanical systems (MEMS). This increased density continues the trend often cited as Moore's Law.

A fab is a common term for where these processes are accomplished. Often the fab is owned by the company that sells the chips, such as Intel, Texas Instruments, or Freescale. A foundry is a fab at which semiconductor chips or wafers are fabricated to order for third party companies that sell the chip, such as fabs owned by Taiwan Semiconductor Manufacturing Company (TSMC), United Microelectronics Corporation (UMC), GlobalFoundries and Semiconductor Manufacturing International Corporation (SMIC).

In 2013 the cost of building the next generation wafer fab was over $10 billion.[1]

WFE market

[edit]Referred to respectively as the wafer fab equipment [2] or wafer front end [3] (equipment) market, both using the acronym WFE, the market is that of the manufacturers of the machines which in turn manufacture semiconductors. The apexresearch link in 2020 identified Applied Materials, ASML, KLA-Tencor, Lam Research, TEL and Dainippon Screen Manufacturing as market participants[2] while the 2019 electronicsweekly.com report, citing The Information Network’s president Robert Castellano, focused on the respective market shares commanded by the two leaders, Applied Materials and ASML.[3]

References

[edit]- ^ Should an Indian fab use older process? Business Standard, 2013

- ^ a b apexresearch, "Global Wafer Fab Equipment (WFE) Market Insights 2019-2025" njmmanews.com, January 30, 2020. Sample apexresearch report (PDF). "Warning: Potential Security Risk Ahead" on the njmmanews.com link to the "Jesus Martinez fills in against Nah-Shon Burrell at Bellator 108" citation in the Nah-Shon Burrell Wikipedia article; no warning on the other links to the njmmanews.com site here in the "Wafer fabrication" Wikipedia article. Retrieved 2020-05-29.

- ^ a b Manners, David, "Applied to lose front-end equipment crown to ASML", electronicsweekly.com, 26 November 2019. Retrieved 2020-05-29.