PCI Express

This article has multiple issues. Please help improve it or discuss these issues on the talk page. (Learn how and when to remove these template messages)

No issues specified. Please specify issues, or remove this template. |

PCI Express logo | |

| Year created | 2004 |

|---|---|

| Created by | Intel |

| Width in bits | 1 |

| No. of devices | 1 per slot |

| Speed | 8 GB/s (v1.1, x32) |

| Style | Serial |

| Hotplugging interface | Depends on form factor |

| External interface | Depends on form factor |

| Website | pcisig |

Template:Distinguish2 PCI Express, officially abbreviated as PCI-E or PCIe, is a computer expansion card interface format introduced by Intel in 2004. PCI Express was designed to replace the general-purpose PCI Local Bus, the high-end PCI-X bus and the AGP graphics card interface. Unlike previous PC expansion interfaces, rather than being a bus it is structured around point-to-point serial links.

Summary

A PCI Express link is built around pairs of serial (1-bit), unidirectional point-to-point connections known as "lanes". This is in sharp contrast to the PCI standard which is a bus-based system in which all the devices share the same bidirectional, 32-bit or 64-bit, parallel signal path.

In PCIe 1.1 (currently the most common version) each lane sends information at a rate of 250 MB/s (250 million bytes per second) in each direction. PCIe 2.0, introduced in late 2007 and found on newer systems such as those based around the Intel X38 or AMD 780G chipsets, doubles this data rate. The latest proposed PCIe 3.0 standard, tentatively scheduled for release around 2010[1], will increase the speed of the links further.

Each PCIe slot carries either one, two, four, eight, sixteen or thirty-two lanes of data between the motherboard and the addin card. Lane counts are written with an "x" prefix e.g. x1 for a single-lane card and x16 for a sixteen-lane card. Thirty-two lanes of 250 MB/s (PCIe 1.1) gives a maximum transfer rate of 8 GB/s (250 MB/s x 32, i.e., 8 billion bytes per second) in each direction. However, the largest size in common use for PCIe 1.1 is x16, giving a transfer rate of 4 GB/s (250 MB/s x 16) in each direction. Putting this into perspective, a single lane for PCIe 1.1 has nearly twice the data rate of normal PCI, a four-lane slot has a transfer rate comparable to the fastest version of the old parallel PCI-X 1.0, and an eight-lane slot has a transfer rate comparable to the fastest version of AGP. However, the data rates cited must be derated because 8b/10b encoding is used in the physical layer. The link transfer speeds cited are to be considered maximum theoretical data rates.

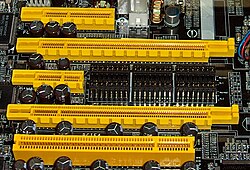

PCIe slots come in a variety of physically different sizes referred to by the maximum lane count they support, ie. x1, x2, x4, x8, x16 and x32. A PCIe card will fit into a slot of its size or bigger, but not into a smaller PCIe slot.

The number of lanes actually connected to a slot may also be less than the number supported by the physical slot size. An example is a x8 slot that actually only runs at x1; these slots will allow any x1, x2, x4 or x8 card to be used, though only running at the x1 speed. This type of socket is described as a 'x8 (x1 mode)' slot, meaning it physically accepts up to x8 cards but only runs at x1 speed. The advantage gained is that a larger range of PCIe cards can still be used without requiring the motherboard hardware to support the full transfer rate - in so doing keeping design and implementation costs down.

The number of lanes is "negotiated" during power-up or explicitly during operation. By making the lane count flexible a single standard can provide for the needs of high-bandwidth cards (e.g. graphics cards, 10 Gigabit Ethernet cards and multiport Gigabit Ethernet cards) while also being economical for less demanding cards. This feature allows a x1 card to be inserted into a x4 slot. The system will decrease the link speed to the x1 card's needs and provide data to the card on one lane even though the motherboard is capable of x4 operation on that particular slot.

As well as the ordinary expansion cards for desktops and servers, the PCIe electrical interface is used in a variety of other form factors including the ExpressCard laptop expansion card interface. PCIe is also often used to connect integrated peripherals on the motherboard.

Specifications of the format are being maintained and developed by a group of more than 900 industry-leading companies called the PCI Special Interest Group (PCI-SIG).

Overview

The PCIe physical layer consists of a network of serial interconnects. A hub on the mainboard acts as a crossbar switch allowing point-to-point device interconnections to be rerouted on the fly. This dynamic point-to-point connection behavior leads to parallelism since more than one pair of devices may communicate with each other at the same time. (In contrast, older PC interfaces had all devices permanently wired to the same bus; therefore, only one device could talk at a time.) This is similar to the difference between conversing over a telephone where you can only call one person at a time, and conversing in a meeting, where you can talk to a person beside you directly. The format also allows channel grouping, where multiple lanes are bonded to a single device pair in order to provide higher bandwidth.

The bonded serial format was chosen over a traditional parallel format due to the phenomenon of timing skew. Timing skew is a direct result of the limitations imposed by the speed of an electrical signal traveling down a wire, which it does at a finite speed. Because different traces in an interface have different lengths, parallel signals transmitted simultaneously from a source arrive at their destinations at different times. When the interconnection clock rate rises to the point where the wavelength of a single bit is less than this difference in path length, the bits of a single word do not arrive at their destination simultaneously, making parallel recovery of the word difficult. Thus, the speed of the electrical signal, combined with the difference in length between the longest and shortest trace in a parallel interconnect, leads to a naturally imposed maximum bandwidth. Serial channel bonding avoids this issue by not requiring the bits to arrive simultaneously. PCIe is just one example of a general trend away from parallel buses to serial interconnects. For other examples, see HyperTransport, Serial ATA, USB, SAS, FireWire or RapidIO. The multichannel serial design also increases flexibility by allowing slow devices to be allocated fewer lanes than fast devices.

PCIe is supported primarily by Intel, which started working on the standard as the Arapahoe project after pulling out of the InfiniBand system. PCIe is intended to be used as a local interconnect only. It was designed to be software compatible with the preexisting Conventional PCI standard, making the conversion of conventional PCI cards and systems to PCI Express as simple as replacing the physical layer without requiring a change to the supporting software. The increased bandwidth on PCI Express has led to unification, as it is fast enough to replace almost all existing internal buses, including AGP and conventional PCI. Intel envisions a single PCI Express controller talking to all external devices in the future, as opposed to the northbridge/southbridge solution used in current machines.

Unlike preceding PC expansion interface standards, being the PCIe a point-to-point connection, removes the need for "arbitrating" the bus or waiting for the bus to be free. This means that while standard PCI-X (133 MHz 64 bit) and PCIe x4 have roughly the same data transfer rate, PCIe x4 will give better performance if multiple device pairs are communicating simultaneously or if communication within a single device pair is bidirectional.

History

While in development, PCI Express (PCIe) was initially referred to as HSI (for High Speed Interconnect), and underwent a name change to 3GIO (for 3rd Generation I/O) before finally settling on its PCI-SIG name PCI Express. It was first drawn up by a technical working group named the Arapahoe Work Group (AWG) which for initial drafts consisted of an Intel only team of architects. Subsequently the AWG was expanded to include industry partners.

PCIe is a technology under constant development and improvement. The current standard version in general use at time of writing is PCIe 1.1; however, the PCI-SIG announced the availability of the PCI Express Base 2.0 specification on 15 January 2007. PCIe 2.0 doubles the data rate of each lane from 2.5 GT/s to 5 GT/s. PCIe 2.0 is backward compatible with PCIe 1.1 as a physical interface slot and from within software, so older cards will still be able to work in machines fitted with this new version. Further information on PCIe 2.0 is detailed below.

Hardware protocol summary

The PCIe link is built around dedicated unidirectional couples of serial (1-bit), point-to-point connections known as "lanes". This is in sharp contrast to the conventional PCI connection, which is a bus-based system where all the devices share the same bidirectional, 32-bit (or 64-bit), parallel bus.

PCI Express is a layered protocol, consisting of a Transaction Layer, a Data Link Layer, and a Physical Layer. The Data Link Layer is further divided to include a Media Access Control sublayer. The Physical Layer is further divided into a logical sublayer and an electrical sublayer. The PHY logical sublayer contains a Physical Coding Sublayer (PCS). (Terms borrowed from the IEEE 802 model of networking protocol.)

Physical Layer

The PCIe Physical Layer (PHY) (PCIEPHY , PCI Express PHY or PCIe PHY) specification is divided into two sublayers, corresponding to electrical and logical specifications. The logical sublayer is sometimes further divided into a MAC (Media Access Control) sublayer and a PCS (Physical Coding Sublayer), although this division is not formally part of the PCIe specification. A specification published by Intel, the PHY Interface for PCI Express (PIPE)[2] , defines the MAC/PCS functional partitioning and the interface between these two sublayers. The PIPE specification also identifies the PMA (Physical Media Attachment) layer, which includes the Serializer/Deserializer and other analog circuitry; however, since SerDes implementations vary greatly among ASIC vendors, PIPE does not specify an interface between the PCS and PMA.

At the electrical level, each lane consists of two unidirectional LVDS or PCML pairs at 2.525 Gbit/s. Transmit and receive are separate differential pairs, for a total of 4 data wires per lane.

A connection between any two PCIe devices is known as a "link", and is built up from a collection of 1 or more lanes. All devices must minimally support single-lane (x1) link. Devices may optionally support wider links composed of 2, 4, 8, 12, 16, or 32 lanes. This allows for very good compatibility in two ways:

- a PCIe card will physically fit (and work correctly) in any slot that is at least as large as it is (e.g. an x1 sized card will work in any sized slot);

- a slot of a large physical size (e.g. x16) can be wired electrically with fewer lanes (e.g. x1, x4, or x8) as long as it provides the power and ground connections required by the larger physical slot size.

In both cases, PCIe will negotiate the highest mutually supported number of lanes.

Even though the two would be signal-compatible, it is not usually possible to place a physically larger PCIe card (e.g. a 16x sized card) into a smaller slot - though some motherboards have open-ended PCIe slots that will allow this.

The width of a PCIe connector is 8.8 mm, while the height is 11.25 mm, and the length is variable. The 'minor' half of the connector is 11.65 mm in length and contains 22 pins, while the length of the 'major' half is variable. The thickness of the card going into the connector is 1.8mm.[3][4]

| Lanes | Pins Total | Pins in 'major' half | Total Length | Length of 'major' half |

|---|---|---|---|---|

| x1 | 36 | 14 | 25 mm | 7.65 mm |

| x4 | 64 | 42 | 39 mm | 21.65 mm |

| x8 | 98 | 76 | 56 mm | 38.65 mm |

| x16 | 164 | 142 | 89 mm | 71.65 mm |

Data transmission

PCIe sends all control messages, including interrupts, over the same links used for data. The serial protocol can never be blocked, so latency is still comparable to conventional PCI, which has dedicated interrupt lines.

Data transmitted on multiple-lane links is interleaved, meaning that each successive byte is sent down successive lanes. The PCIe specification refers to this interleaving as "data striping." While requiring significant hardware complexity to synchronize (or deskew) the incoming striped data, striping can significantly increase the throughput of the link. Due to padding requirements, striping may not necessarily reduce the latency of small data packets on a link.

As with all high data rate serial transmission protocols, clocking information must be embedded in the signal. At the physical level, PCI Express utilizes the very common 8b/10b encoding scheme to ensure that strings of consecutive ones or consecutive zeros are limited in length. This is necessary to prevent the receiver from losing track of where the bit edges are. In this coding scheme every 8 (uncoded) payload bits of data are replaced with 10 (encoded) bits of transmit data, consuming an extra 25% of the overall electrical bandwidth.

Many other protocols (such as SONET) use a different form of encoding known as "scrambling" to embed clock information into data streams. The PCI Express specification also defines a scrambling algorithm, but it is used to reduce EMI (Electromagnetic interference) by preventing repeating data patterns in the transmitted data stream.

Signaling rate

The first-generation PCIe transfers data at a 2.5 GT/s (gigatransfer per second) signaling rate per lane. PCIe version 2.0 provides an increase in the signaling rate to 5 GT/s per lane. A third-generation PCIe specification is in development with the goal of further increasing the rate.

Data Link Layer

The Data Link Layer implements the sequencing of the Transaction Layer Packets (TLPs) that are generated by the Transaction Layer, data protection via a 32-bit cyclic redundancy check code (CRC, known in this context as LCRC) and an acknowledgment protocol (ACK and NAK signaling). TLPs that pass an LCRC check and a sequence number check result in an acknowledgment, or ACK, while those that fail these checks result in a negative acknowledgment, or NAK. TLPs that result in a NAK, or timeouts that occur while waiting for an ACK, result in the TLPs being replayed from a special buffer in the transmit data path of the Data Link Layer. This guarantees delivery of TLPs in spite of electrical noise, barring any malfunction of the device or transmission medium.

ACK and NAK signals are communicated via a low-level packet known as a data link layer packet, or DLLP. DLLPs are also used to communicate flow control information between the transaction layers of two connected devices, as well as some power management functions.

Transaction Layer

PCI Express implements split transactions (transactions with request and response separated by time), allowing the link to carry other traffic while the target device gathers data for the response.

PCI Express utilizes credit-based flow control. In this scheme, a device advertises an initial amount of credit for each of the receive buffers in its Transaction Layer. The device at the opposite end of the link, when sending transactions to this device, will count the number of credits consumed by each TLP from its account. The sending device may only transmit a TLP when doing so does not result in its consumed credit count exceeding its credit limit. When the receiving device finishes processing the TLP from its buffer, it signals a return of credits to the sending device, which then increases the credit limit by the restored amount. The credit counters are modular counters, and the comparison of consumed credits to credit limit requires modular arithmetic. The advantage of this scheme (compared to other methods such as wait states or handshake-based transfer protocols) is that the latency of credit return does not affect performance, provided that the credit limit is not encountered. This assumption is generally met if each device is designed with adequate buffer sizes.

First-generation PCIe is often quoted to support a data rate of 250 MB/s in each direction, per (x1) lane. This figure is a calculation from the physical signaling rate (2.5 Gbaud) divided by the encoding overhead (10 bits per byte.) This means a sixteen lane (x16) PCIe card would then be theoretically capable of 250 MB/s * 16 = 4 GB/s in each direction. While this is correct in terms of data bytes, more meaningful calculations will be based on the usable data payload rate, which depends on the profile of the traffic, which is a function of the high-level (software) application and intermediate protocol levels.

Like other high data rate serial interconnect systems, PCIe has a protocol and processing overhead due to the additional transfer robustness (CRC and Acknowledgments). Long continuous unidirectional transfers (such as those typical in high-performance storage controllers) can approach >95% of PCIe's raw (lane) data rate. These transfers also benefit the most from increased number of lanes (x2, x4, etc.) But in more typical applications (such as a USB or Ethernet controller), the traffic profile is characterized as short data packets with frequent enforced acknowledgments.[citation needed] This type of traffic reduces the efficiency of the link, due to overhead from packet parsing and forced interrupts (either in the device's host interface or the PC's CPU.) This loss of efficiency is not particular to PCIe.

Form factors

- Low height card

- Mini Card: a replacement for the Mini PCI form factor (with x1 PCIe, USB 2.0 and SMBus buses on the connector)

- ExpressCard: successor to the PC card form factor (with x1 PCIe and USB 2.0; hot-pluggable)

- PCI Express ExpressModule: a hot-pluggable modular form factor defined for servers and workstations

- XMC: similar to the CMC/PMC form factor (with x4 PCIe or Serial RapidI/O)

- AdvancedTCA: a complement to CompactPCI for larger applications; supports serial based backplane topologies

- AMC: a complement to the AdvancedTCA specification; supports processor and I/O modules on ATCA boards (x1,x2,x4 or x8 PCIe).

- PCI Express External Cabling[5]

- Mobile PCI Express Module (MXM) A graphics module specification created by NVIDIA.

- Advanced eXpress I/O Module (AXIOM) graphics module design endorsed by ATI Technologies (ATI was purchased by AMD in 2006).

Competing protocols

Several communications standards have emerged based on high bandwidth serial architectures. These include but are not limited to HyperTransport, InfiniBand, RapidIO, StarFabric and Intel QuickPath Interconnect.

Essentially the differences are based on the tradeoffs between flexibility and extensibility vs. latency and overhead. An example of such a tradeoff is adding complex header information to a transmitted packet to allow for complex routing (PCI Express is not capable of this). This additional overhead reduces the effective bandwidth of the interface and complicates bus discovery and initialization software. Also making the system hot-pluggable requires that software track network topology changes. Examples of buses suited for this purpose are InfiniBand and StarFabric.

Another example is making the packets shorter to decrease latency (as is required if a bus is to be operated as a memory interface). Smaller packets mean that the packet headers consume a higher percentage of the packet, thus decreasing the effective bandwidth. Examples of bus protocols designed for this purpose are RapidIO and HyperTransport.

PCI Express falls somewhere in the middle, targeted by design as a system interconnect (local bus) rather than a device interconnect or routed network protocol. Additionally, its design goal of software transparency constrains the protocol and raises its latency somewhat.

Status

PCI Express has replaced AGP as the default interface for graphics cards on new systems. With a few exceptions, all graphics cards being released today (2008) from ATI and NVIDIA use PCI Express. NVIDIA uses the high bandwidth data transfer of PCIe for its Scalable Link Interface (SLI) technology, which allows multiple graphics cards of the same chipset and model number to be run in tandem, allowing increased performance. ATI also has developed a multi-GPU system based on PCIe called CrossFire. Eventually AMD and nVidia released motherboard chipsets, which supports up to four PCIe x16 slots, allowing tri-GPU and quad-GPU card configurations.

Uptake for other forms of PC expansion has been much slower and conventional PCI remains dominant. PCI Express is commonly used for disk array controllers, onboard gigabit ethernet and wi-fi but add-in cards are still generally conventional PCI, particularly at the lower end of the market. Sound cards, modems, serial port cards and other cards with low-speed interfaces are still nearly all conventional PCI. For this reason most motherboards supporting PCI Express offer conventional PCI slots as well.

ExpressCard has been introduced on several mid- to high-range laptops such as Apple's MacBook Pro line. Unlike desktops, however, laptops frequently only have one expansion slot. Replacing the PC card slot with ExpressCard slot means a loss in compatibility with PC-card devices.

External PCI Express

The name used by PCI-SIG (PCI Special Interest Group) is PCI Express External Cabling. The most commonly used name is External PCI Express or shortened External PCIe. Another name used is Cabled PCI Express (2400 Google-hits, 2008-03) or shortened Cabled PCIe.

Specifications

2007-02 The first PCI Express External Cabling specifications was released by PCI-SIG February 2007. "This specification helps the industry create new products that will take PCIe technology out of the box – enabling PCIe solutions for IO expansion drawers, external graphics processors, tethered mobile docking, communications equipment and embedded applications".

Standard cables and connectors have been defined for x1, x4, x8, and x16 link widths, with a transfer rate of 250 MB/s per lane. The PCI-SIG also expects the norm will evolve to reach the 500 MB/s as found in PCI Express 2.0. The maximum cable length hasn't been determined yet.

External PCIe Video Cards

Potentially External PCIe could give a notebook the graphic power of a desktop, by connecting a notebook with any PCIe desktop video card (enclosed in its own external housing), however, only one finalized product and two concept products exist. All three deliver the power of the video card to external displays only, and all connect to a notebook through an ExpressCard interface which limits the bandwidth from an inserted x16 video card (4 GB/s in each direction), to just x1 (250 MB/s in each direction): Magma ExpressBox Magma. Luxium by MSI TheInquirer, CustomPcMag. XG Station by Asus Asus, VR-Zone

Additionally, Nvidia has developed Quadro Plex, external PCIe Video Cards that can be used for advanced graphic applications. These video cards require a PCI Express x8 or x16 slot, for the interconnection cable.[6] AMD has recently announced the ATI XGP technology based on proprietary cabling solution which is compatible with PCIe signal tranmissions.[7]

PCI Express 2.0

PCI-SIG announced the availability of the PCI Express Base 2.0 specification on 15 January 2007.[8] PCIe 2.0 doubles the bus standard's bandwidth from 0.25 GByte/s to 0.5 GByte/s, meaning a x32 connector can transfer data at up to 16 GByte/s in each direction.

PCIe 2.0 is backward compatible with PCIe v1.x. Graphic cards and motherboards designed for v2.0 will be able to work with v1.1 and v1.0.

The PCI-SIG also said PCIe 2.0 also features improvements to the point-to-point data transfer protocol and its software architecture.[9]

In June 2007 Intel released the specification of the Intel P35 chipset which does not support PCIe 2.0 only PCIe 1.1.[10] Some people may be confused by the P35 block diagram[11] which states the Intel P35 has a PCIe x16 graphics link (8 GB/s) and 6 PCIe x1 links (500 MB/s each), for simple verification one can view the P965 block diagram which shows the same number of lanes and bandwidth but was released before PCIe 2.0 was finalized. Intel's first PCIe 2.0 capable chipset was the X38 and boards where already shipping from various vendors (Abit, Asus, Gigabyte) as of October 21, 2007.[12] AMD started supporting PCIe 2.0 with its RD700 chipset series and nVidia started with the MCP72.[13] The specification of the Intel P45 chipset includes PCIe 2.0 .

PCI Express 3.0

In August 2007 PCI-SIG announced that PCI Express 3.0 will carry a bit rate of 8 gigatransfers per second. The spec will be backwards-compatible with existing PCIe implementations and a final spec is due in 2009. New features for PCIe 3.0 specification include a number of optimizations for enhanced signaling and data integrity, including transmitter and receiver equalization, PLL improvements, clock data recovery, and channel enhancements for currently supported topologies.[1]

Following a six-month technical analysis of the feasibility of scaling the PCIe interconnect bandwidth, PCI-SIG's analysis found out that 8 gigatransfers per second can be manufactured in mainstream silicon process technology, and can be deployed with existing low-cost materials and infrastructure, while maintaining full compatibility (with negligible impact) to the PCIe protocol stack.

PCIe 2.0 delivers 5 GT/s but employed an 8b/10b encoding scheme which took 20 percent overhead on the overall raw bit rate. By removing the requirement for the 8b/10b encoding scheme (relying solely on the still-used scrambler), PCIe 3.0's 8 GT/s bit rate effectively delivers double PCIe 2.0 bandwidth. According an official press release by PCI-SIG on August 8, 2007:

"The final PCIe 3.0 specifications, including form factor specification updates, may be available by late 2009, and could be seen in products starting in 2010 and beyond."[14]

PCI-SIG expects the PCIe 3.0 specifications to undergo rigorous technical vetting and validation before being released to the industry. This process, which was followed in the development of prior generations of the PCIe Base and various form factor specifications, includes the corroboration of the final electrical parameters with data derived from test silicon and other simulations conducted by multiple members of the PCI-SIG.

See also

- Industry Standard Architecture (ISA)

- Extended Industry Standard Architecture (EISA)

- Micro Channel architecture (MCA)

- NuBus

- VESA Local Bus (VLB)

- Conventional PCI

- Accelerated Graphics Port (AGP)

- List of device bandwidths (A useful listing of device bandwidths that include PCI Express)

- PCI-X

References

- ^ a b "PCI Express 3.0 Bandwidth: 8.0 Gigatransfers/s". ExtremeTech. 2007-08-09. Retrieved 2007-09-05.

- ^ "PHY Interface for the PCI Express Architecture, version 2.00" (PDF). Retrieved 2008-05-21.

- ^ "Mechanical Drawing for PCI Express Connector". Retrieved 2007-12-07.

- ^ "FCi schematic for PCIe connectors" (PDF). Retrieved 2007-12-07.

- ^ "PCI Express External Cabling 1.0 Specification". Retrieved 2007-02-09.

- ^ Quadro Plex website.

- ^ ati.amd.com

- ^ "PCI Express Base 2.0 specification announced" (PDF) (Press release). PCI-SIG. 2007-01-15. Retrieved 2007-02-09.

{{cite press release}}: Check date values in:|date=(help) — note that in this press release the term "aggregate bandwidth" refers to the sum of incoming and outgoing bandwidth; using this terminology the aggregate bandwidth of full duplex 100BASE-TX is 200 Mbit/s - ^ Tony Smith (2006-10-11). "PCI Express 2.0 final draft spec published". The Register. Retrieved 2007-02-09.

{{cite news}}: Check date values in:|date=(help) - ^ "Intel® P35 Express Chipset Product Brief" (PDF). Intel. Retrieved 2007-09-05.

- ^ Richard Swinburne (2007-05-21). "First look - Intel P35 chipset". bit-tech.net. Retrieved 2007-06-19.

{{cite news}}: Check date values in:|date=(help) - ^ Gary Key & Wesley Fink (2007-05-21). "Intel P35: Intel's Mainstream Chipset Grows Up". AnandTech. Retrieved 2007-05-21.

{{cite news}}: Check date values in:|date=(help) - ^ Anh Huynh (2007-02-08). "NVIDIA "MCP72" Details Unveiled". AnandTech. Retrieved 2007-02-09.

{{cite news}}: Check date values in:|date=(help) - ^ "PCI-SIG Announces PCI Express 3.0 Bit Rate For Products In 2010 And Beyond". 2007-08-08. Retrieved 2008-03-24.

{{cite news}}: Cite has empty unknown parameter:|1=(help)