iCE (FPGA)

iCE is the brand name used for a family of low-power field-programmable gate arrays (FPGAs) produced by Lattice Semiconductor. Parts in the family are marketed with the "world's smallest FPGA" tagline, and are intended for use in portable and battery-powered devices (such as mobile phones),[1] where they would be used to offload tasks from the device's main processor or system on chip. By doing so, the main processor and its peripherals can enter a low-power state or be powered off entirely, potentially increasing battery life.

Lattice received the iCE brand as part of its 2011 acquisition of SiliconBlue Technologies.

History

The logo used by SiliconBlue following their being acquired in 2011. | |

| Company type | Private |

|---|---|

| Industry | Integrated circuits |

| Founded | April 12, 2005[2] |

| Founders |

|

| Defunct | December 9, 2011 |

| Fate | Acquired by Lattice Semiconductor |

| Headquarters | , |

| Products | FPGAs |

| Website | www.siliconbluetech.com (archived copy from 2012) |

The iCE brand was originally used by SiliconBlue Technologies Corporation, a former Santa Clara, California-based fabless designer of integrated circuits. SiliconBlue was a start-up founded in 2005 by former employees of Actel, AMD, Lattice, Monolithic Memories, and Xilinx.[2][3] Most notable among the founders was John Birkner, one of the inventors of programmable array logic.[4]

In 2006, SiliconBlue was funded with $16 million in "Series A" capital,[5] and in June 2008 announced the iCE65 L series of devices. The devices were to be fabricated on TSMC's 65 nm CMOS process node, which SiliconBlue claimed would provide reduced power consumption compared to contemporary FPGAs from other manufacturers.[6] In October 2008, SiliconBlue raised a further $24 million in Series B capital.[5]

In 2009, the first iCE65 L devices were shipped to customers.[7] SiliconBlue also registered SiliconBlue Technologies (Hong Kong) Limited, which remains as a subsidiary of Lattice Semiconductor.[8][9]

In 2010, the lowest-end of the iCE65 P devices was announced by SiliconBlue. The devices were claimed to be as much as 30% faster than iCE65 L devices while maintaining similar power consumption.[10][11] In the June of the same year, SiliconBlue closed a $15 million Series C funding round.[12]

In April 2011, SiliconBlue announced that it was to release new product families, code-named "Los Angeles" and "San Francisco," using a TSMC 40 nm process node.[13] The production of devices on a 40 nm process node was further confirmed in June 2011, when SiliconBlue received $18 million in Series D funding to bring 40 nm devices to market.[14][15] The iCE40 product family was officially released in July 2011.[16]

On 9 December 2011, SiliconBlue Technologies was acquired by Lattice Semiconductor in a $63.2 million cash buyout. As part of this buyout, Lattice received the iCE brand, manufacturing capabilities with TSMC, and a licence for various patents from Kilopass Technologies, including for its XPM one-time programmable (OTP) memory technology.[17]: 15, 8, 11

In April 2012, Lattice announced that the iCE65 families would be discontinued.[18] The iCE40 LP and HX device families entered volume production the following month.[19] The iCE40 LP family won the Elektra Digital Semiconductor Product of the Year award for 2012.[20]

In July 2014, the iCE40 Ultra family was announced.[21]

In February 2015, Lattice launched the iCE40 UltraLite device family. The devices in this family are claimed to operate at 30% less power than those of unspecified competitors, and are claimed to be the world's smallest FPGAs, being available in 1.4×1.4 mm packages.[22] The family won the 2015 Elektra Digital Semiconductor Product of the Year award.[23]

In December 2016, Lattice launched the iCE40 UltraPlus device family. UltraPlus devices provide additional memory, additional processing elements, and support for newer interfaces and protocols compared to previous iCE40 Ultra/UltraLite devices.[24][25]

Architecture

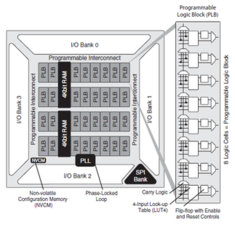

iCE65 and iCE40 devices are constructed as an array of programmable logic blocks (PLBs), where a PLB is a block of eight logic cells. Each logic cell consists of a four-input lookup table (sometimes called a 4-LUT or LUT4) with the output connected to a D flip-flop (a 1-bit storage element). Within a PLB, each logic cell is connected to the following and preceding cell by carry logic, intended to improve the performance of constructs such as adders and subtractors. Interspersed with PLBs are blocks of RAM, each four kilobits in size. The number of RAM blocks varies depending on the device.[26]: . 2-1 to 2-3 [27]: . 5–9

Compared to LUT6-based architectures (such as Xilinx 7-series devices and Altera Stratix devices), a LUT4-based device is unable to implement as-complex logic functions with the same number of logic cells. For example, a logic function with seven inputs could be implemented in eight LUT4s or two LUT6s.

iCE devices use volatile SRAM to store configuration data. As a result, the data must be loaded onto the device each time power is lost. All iCE devices support loading configuration data from a programmer, from an external flash memory chip, or, with the exception of iCE40 LM devices,[28] from a so-called NVCM, or non-volatile configuration memory. The NVCM is a one-time-programmable (OTP) memory integrated into the FPGA to negate the need for an external memory chip. Lattice claims that using the NVCM can improve design security by making reverse engineering more difficult.[29]

The I/O pins on iCE devices are separated into up to four banks. On some devices each bank has its own power-supply pin (labelled VCCIO), allowing the logic-high voltage level of the I/O bank to be adjusted.[26]: 2–7 Configurable I/O voltage levels are used by iCE devices to allow support for multiple interface standards with voltage levels between 1.8 V and 3.3 V, such as LVDS.[26]: 3–1 iCE65 devices also listed being able to support SSTL through this method.[27]: 11

Development

iCE FPGAs, as with most FPGAs and CPLDs, are typically designed for using a hardware description language (HDL), which describes an electronic circuit. Lattice iCEcube2, the IDE provided by Lattice for developing on their FPGAs, supports the VHDL and Verilog languages, as well as the EDIF format.

Open source

The details of a specific FPGA's bitstream format (which defines how the internal elements of the FPGA are connected and interact with each other) are not usually published by FPGA vendors. This means that, generally, an engineer creating a design for an FPGA must use the tools provided by the FPGA's manufacturer.

In December 2015, at 32C3,[30] Project IceStorm, a toolchain consisting of Yosys (Verilog synthesis frontend), Arachne-pnr (place and route and bitstream generation), and icepack (plain text-to-binary bitstream conversion) tools was presented by Claire Wolf, one of the two developers (along with Mathias Lasser) of the toolchain.[31] The toolchain is notable for being one of, if not the only, fully open-source toolchains for FPGA development. At the same December 2015 presentation, Wolf also demonstrated a RISC-V SoC design built using the open-source toolchain and running on an iCE40 HX8K device. As of March 2021, the toolchain supports iCE40 LP/HX 1K/4K/8K and UP devices.[32]

List of iCE devices

iCE65 (65 nm)

The iCE65 name was used by SiliconBlue Technologies for the devices it designed for a 65 nm process node. Following the acquisition of SiliconBlue in 2011, the name was used by Lattice Semiconductor until the family was discontinued in April 2012.[18]

iCE65 L

| Series | Device | LEs | RAM | PLLs | Max. I/Os |

|---|---|---|---|---|---|

| iCE65 L | L01 | 1280 | 64 kbit | — | 95 |

| L04 | 3520 | 80 kbit | 176 | ||

| L08 | 7680 | 128 kbit | 222 | ||

| L16 | 16 896 | 384 kbit | Unknown | ||

| iCE65 P | P04 | 3520 | 80 kbit | 1 | 174 |

| P08 | 7680 | 128 kbit | 2 | Unknown | |

| P12 | 12 160 | 160 kbit | 2 | Unknown |

The iCE65 L series of devices was intended for low-power applications and handheld devices. The series was first announced in mid 2008,[6] and first shipped to volume customers in early 2009.[7]

Information about a larger device in the series, the iCE65L16, was listed on the SiliconBlue website in 2010,[33] but no mention is made in a 2012 revision of the L-series datasheet.[27] It is unclear whether the device was ever produced commercially.

iCE65 P

The iCE65 P-series devices were marketed as a higher-performance version of the L-series devices, intended for use in display, memory, and SERDES applications,[34] and were announced in early 2010.[10][11] Three devices were listed as being part of the series but only one device, the lowest-end iCE65P04, was fully specified. The latest datasheet for the family, published in 2011, lists the other two parts but does not give specifications.[35] Whether these other two devices were ever commercially produced is unclear.

iCE40 (40 nm)

Lattice uses the iCE40 name for its iCE-branded devices produced on a 40 nm process node. The company has also used the codename "Los Angeles" in press releases. The iCE40 family was launched in July 2011 with iCE40 LP and HX parts,[16] and was updated in July 2014 with the iCE40 Ultra parts,[21] in February 2015 with the iCE40 UltraLite parts,[22] and in December 2016 with the iCE40 UltraPlus parts.[24]

iCE40 Ultra, UltraLite, & UltraPlus

| Family | Device | LEs | RAM | I²C | SPI | DSP | PWM | Max. I/Os |

|---|---|---|---|---|---|---|---|---|

| UltraLite | UL640 | 640 | 56 kbit | 2 | — | 26 | ||

| UL1K | 1280 | 56 kbit | 2 | 26 | ||||

| Ultra | iCE5LP1K | 1100 | 64 kbit | 1 | 1 | 2 | 39 | |

| iCE5LP2K | 2048 | 80 kbit | 2 | 2 | 4 | 39 | ||

| iCE5LP4K | 3520 | 80 kbit | 2 | 2 | 4 | 39 | ||

| UltraPlus | UP3K | 2800 | 1104 kbit | 2 | 2 | 4 | 21 | |

| UP5K | 5280 | 1144 kbit | 2 | 2 | 8 | 39 | ||

The iCE40 Ultra, UltraLite, and UltraPlus devices are intended for applications with especially low limits on available space and power, such as in wearable technology and smart watches.[21] They are offered in chip-scale, BGA, and QFN packages, with dimensions from 1.4×1.4 mm to 7×7 mm. All devices in family integrate one or two I²C hard cores, with Ultra and UltraPlus devices also including hard SPI bus cores and DSP blocks. UltraLite devices are claimed to operate at half the static current draw of Ultra devices (35 μA compared to 71 μA). Most devices in the family also include a PWM controller, intended to be used to drive IR or RGB LEDs.[36]: 5

Lattice launched the Ultra family in mid 2014,[21] and the UltraLite family in early 2015.[22] In 2015, the UltraLite family won the Elektra Digital Semiconductor Product of the Year award.[23]

In September 2016, the Apple iPhone 7 was released and made use of an iCE5LP4K device.[37]

In December 2016, Lattice launched the UltraPlus family intended for distributed processing and so-called "mobile heterogeneous computing." The devices include a 1 Mbit (4×256 kbit) single-port RAM (compare with dual-ported RAM), additional DSP processing elements, and support for additional interfaces, such as MIPI I3C, D-PHY, and Virtual GPIO.[24][25]

iCE40 LP & LM

| Family | Device | LEs | RAM | I²C | SPI | PLLs | Max. I/Os |

|---|---|---|---|---|---|---|---|

| LP | LP384 | 384 | — | 39 | |||

| LP640 | 640 | 32 kbit | 11 | ||||

| LP1K | 1280 | 64 kbit | 1 | 97 | |||

| LP4K | 3520 | 80 kbit | 2 | 180 | |||

| LP8K | 7680 | 128 kbit | 2 | 180 | |||

| LM | LM1K | 1100 | 64 kbit | 2 | 2 | 1 | 39 |

| LM2K | 2048 | 80 kbit | 2 | 2 | 1 | 39 | |

| LM4K | 3520 | 80 kbit | 2 | 2 | 1 | 39 | |

The iCE40 LP (low power) and LM (low power with hard IP) parts are intended for use in battery-powered devices as hardware accelerators and I/O port expanders, and for use in the same applications as iCE40 Ultra and UltraLite parts. Compared to the Ultra parts, LP and LM parts are available in a wider range of footprints, offer a greater number of resources (I/O pins, embedded RAM, and logic elements), but consume more power.[28]

LP devices differ from the Ultra devices in that they do not include hard IP cores. Instead, any interface logic must be implemented in the FPGA fabric. This is generally less preferable, as so-called "soft cores" are less power-efficient than hard cores, and often are unable to operate at the same frequencies. A soft core also reduces the number of logic cells available to the application. LM devices integrate two I²C and two SPI hard cores, as well as two strobe generators. Most LP and LM devices integrate one or two phase-locked loops.

The families were launched in mid 2011 and entered volume production in mid 2012.[16][19] They won the Elektra Digital Semiconductor Product of the Year award for 2012.[20] In 2015, it was announced that ZTE would use LM devices to provide sensor hub and infrared remote control functionality in its Star 2 smartphone.[38]

iCE40 HX

| Device | LEs | RAM | PLLs | Static current | Max. I/Os |

|---|---|---|---|---|---|

| HX1K | 1280 | 64 kbit | 1 | 296 μA | 98 |

| HX4K | 3520 | 80 kbit | 2 | 1140 μA | 109 |

| HX8K | 7680 | 128 kbit | 2 | 1140 μA | 208 |

The iCE40 HX devices are intended for high-performance applications. Compared to iCE40 LP and Ultra devices, they offer lower maximum propagation delay (7.30 ns versus 9.00–9.36 ns),[26]: 3–13, 3–15 and more I/O pins. HX series devices consume significantly more static power and are available only in significantly larger footprints compared to Ultra and LP parts (7×7 mm to 2×2 cm). Similarly to the LP devices, HX parts do not provide hard IP cores, but do provide one or two phase-locked loops. Unlike other iCE40 devices, the HX parts are also available in QFP footprints.[28]

The HX parts were launched in mid 2011 alongside the LP parts,[16] and entered volume production in mid 2012.[19]

See also

References

- ^ "iCE40 Ultra / UltraLite - Lattice Semiconductor". Lattice Semiconductor. Archived from the original on March 8, 2016. Retrieved 5 April 2016.

{{cite web}}: CS1 maint: unfit URL (link) - ^ a b c California Secretary of State Business Search, entity number C2632216.

- ^ "SiliconBlue Team". SiliconBlue Technologies. 2006. Archived from the original on 6 December 2006. Retrieved 13 May 2016.

{{cite web}}: CS1 maint: unfit URL (link) - ^ "1978: PAL User-Programmable Logic Devices Introduced". The Silicon Engine - A Timeline of Semiconductors in Computers. Computer History Museum. Archived from the original on 1 April 2016. Retrieved 13 May 2016.

- ^ a b "SiliconBlue Secures $24 Million in Series-B Funding" (Press release). SiliconBlue Technologies. 22 October 2008. Archived from the original on 13 May 2016. Retrieved 13 May 2016.

- ^ a b "SiliconBlue Pioneers New FPGA Technology for Handheld, Ultra-Low Power Applications". SiliconBlue Technologies. 2 June 2008. Archived from the original on 9 April 2016. Retrieved 9 April 2016.

- ^ a b "SiliconBlue announces volume production shipments of iCE65 ultra-low-power FPGAs". EETimes. 9 February 2009. Archived from the original on April 6, 2016. Retrieved 6 April 2016.

{{cite web}}: CS1 maint: unfit URL (link) - ^ Company Particulars Search - ICRIS CSC Companies Registry, CR number 1330814.

- ^ "Exhibit 21.1 - Subsidiaries of the Registrant". US Securities and Exchange Commission. 2 March 2016. Retrieved 13 May 2016.

- ^ a b "SiliconBlue Enables Differentiated Mobile Broadband Products with New P-Series mobileFPGA Devices" (Press release). Reuters. 15 February 2010. Archived from the original on 17 November 2010. Retrieved 6 April 2016.

- ^ a b "SiliconBlue unveils new series of FPGAs targeting mobile apps". EETimes. 17 February 2010. Archived from the original on 13 May 2016. Retrieved 13 May 2016.

- ^ "SiliconBlue Completes $15M Series C Preferred Stock Financing" (Press release). BusinessWire. 7 June 2010. Archived from the original on 13 May 2016. Retrieved 13 May 2016.

- ^ Clarke, Peter (5 April 2011). "SiliconBlue tips FPGA move to 40-nm". EETimes. Archived from the original on 13 May 2016. Retrieved 13 May 2016.

- ^ "SiliconBlue Raises $18 Million in Series D Funding" (Press release). BusinessWire. 29 June 2011. Archived from the original on 7 May 2012. Retrieved 13 May 2016.

- ^ Wauters, Robin (29 June 2011). "SiliconBlue Scores $18 Million in Series D Funding". TechCrunch. Archived from the original on 10 March 2016. Retrieved 13 May 2016.

- ^ a b c d Maxfield, Clive (11 July 2011). "SiliconBlue launches 40nm mobileFPGA family (code name "Los Angeles")". EETimes. Archived from the original on 13 May 2016. Retrieved 13 May 2016.

- ^ Form 10-K - Lattice Semiconductor Corporation. US Securities and Exchange Commission. 2012.

- ^ a b PCN# 08B-12: Notification of Intent to Discontinue the iCE65 Product Family. Lattice Semiconductor. 2012.

- ^ a b c "Lattice Announces Production Release Of iCE40 Los Angeles LP-Series And HX-Series mobileFPGA Device Families". Lattice Semiconductor. 8 May 2012. Archived from the original on March 31, 2016. Retrieved 5 April 2016.

{{cite web}}: CS1 maint: unfit URL (link) - ^ a b "2012 Winners :: Elektra Awards". Electronics Weekly. Archived from the original on April 6, 2016. Retrieved 6 April 2016.

{{cite web}}: CS1 maint: unfit URL (link) - ^ a b c d "Lattice Semiconductor Launches iCE40 Ultra™ Platform for Wearable Device Development". Lattice Semiconductor. 1 December 2015. Archived from the original on March 31, 2016. Retrieved 5 April 2016.

{{cite web}}: CS1 maint: unfit URL (link) - ^ a b c "Lattice Semiconductor's New iCE40 UltraLite Device Enables OEMs to Accelerate Time-to-Market of Feature-Rich Mobile Devices". Lattice Semiconductor. 3 February 2015. Archived from the original on March 31, 2016. Retrieved 5 April 2016.

{{cite web}}: CS1 maint: unfit URL (link) - ^ a b "2015 Winners :: Elektra Awards". Electronics Weekly. Archived from the original on April 5, 2016. Retrieved 5 April 2016.

{{cite web}}: CS1 maint: unfit URL (link) - ^ a b c "New iCE40 UltraPlus Devices from Lattice Semiconductor Accelerate Customer Innovation in Smartphones and IoT Edge Devices" (Press release). Lattice Semiconductor. 12 December 2016. Archived from the original on 28 May 2017. Retrieved 28 May 2017.

- ^ a b Maxfield, Max (22 December 2016). "Lattice introduces iCE40 UltraPlus high-performance low-power FPGAs". EETimes. Archived from the original on 30 January 2017. Retrieved 28 May 2017.

- ^ a b c d DS1040 - iCE40 LP/HX Family Data Sheet v3.2. Lattice Semiconductor. 2015.

- ^ a b c iCE65™ Ultra Low-Power mobileFPGA™ Family Datasheet v2.42. Lattice Semiconductor. 2012.

- ^ a b c "iCE40 LP/HX/LM - Lattice Semiconductor". Lattice Semiconductor. Archived from the original on March 25, 2016. Retrieved 6 April 2016.

{{cite web}}: CS1 maint: unfit URL (link) - ^ Lattice TN1248 - iCE40 Programming and Configuration v2.8. Lattice Semiconductor. 2015.

- ^ "Schedule 32. Chaos Communication Congress". Chaos Computer Club. Archived from the original on January 8, 2016. Retrieved 8 April 2016.

{{cite web}}: CS1 maint: unfit URL (link) - ^ Wolf, Claire; Lasser, Matthias. "Project IceStorm". Retrieved March 6, 2021.

In papers and reports, please refer to Project IceStorm as follows: Claire Wolf, Mathias Lasser. Project IceStorm.

{{cite web}}: CS1 maint: url-status (link) - ^ "Project IceStorm". Claire Wolf. Archived from the original on March 6, 2021.

{{cite web}}: CS1 maint: unfit URL (link) - ^ "SiliconBlue Technologes: iCE65 L-Series". SiliconBlue Technologies. Archived from the original on February 20, 2010. Retrieved 6 April 2016.

{{cite web}}: CS1 maint: unfit URL (link) - ^ The iCE65 mobileFPGA Family Product Table v1.1. Lattice Semiconductor.

- ^ iCE65™ P-Series Ultra Low-Power mobileFPGA™ Family v1.31. SiliconBlue Technologies. 22 April 2011.

- ^ TN 1288 - iCE40 LED Driver Usage Guide. Lattice Semiconductor. 2014.

- ^ "Apple iPhone 7 Teardown | Chipworks". Chipworks Inc. 15 September 2016. Archived from the original on 16 September 2016. Retrieved 17 September 2016.

- ^ "ZTE Chooses Lattice Semiconductor for Feature Differentiation and Integration on Star 2 Smartphone". Reuters. 23 June 2015. Archived from the original on 6 April 2016. Retrieved 6 April 2016.