Field-effect transistor: Difference between revisions

| Line 159: | Line 159: | ||

</ref> |

</ref> |

||

The fragile insulating layer of the MOSFET between the gate and channel makes it vulnerable to [[electrostatic discharge|electrostatic damage]] during handling. This is not usually a problem after the device has been installed in a properly designed circuit. |

The fragile insulating layer of the MOSFET between the gate and channel makes it vulnerable to [[electrostatic discharge|electrostatic damage]] during handling. This is not usually a problem after the device has been installed in a properly designed circuit. |

||

watu wa environmental and biosystems had done this assignment...kidenge |

|||

aefhh |

|||

== Uses of FET== |

== Uses of FET== |

||

Revision as of 11:52, 21 February 2014

This article needs additional citations for verification. (December 2010) |

The field-effect transistor (FET) is a transistor that uses an electric field to control the shape and hence the conductivity of a channel of one type of charge carrier in a semiconductor material. FETs are unipolar transistors as they involve single-carrier-type operation. The concept of the FET predates the bipolar junction transistor (BJT), though it was not physically implemented until after BJTs due to the limitations of semiconductor materials and the relative ease of manufacturing BJTs compared to FETs at the time.

History

The field-effect transistor was first patented by Julius Edgar Lilienfeld in 1926 and by Oskar Heil in 1934, but practical semiconducting devices (the JFET) were developed only much later after the transistor effect was observed and explained by the team of William Shockley at Bell Labs in 1947. The MOSFET, which largely superseded the JFET and had a more profound effect on electronic development, was invented by Dawon Kahng and Martin Atalla in 1960.[1]

Basic information

FETs can be majority-charge-carrier devices, in which the current is carried predominantly by majority carriers, or minority-charge-carrier devices, in which the current is mainly due to a flow of minority carriers.[2] The device consists of an active channel through which charge carriers, electrons or holes, flow from the source to the drain. Source and drain terminal conductors are connected to the semiconductor through ohmic contacts. The conductivity of the channel is a function of the potential applied across the gate and source terminals.

The FET's three terminals are:[3]

- Source (S), through which the carriers enter the channel. Conventionally, current entering the channel at S is designated by IS.

- Drain (D), through which the carriers leave the channel. Conventionally, current entering the channel at D is designated by ID. Drain-to-source voltage is VDS.

- Gate (G), the terminal that modulates the channel conductivity. By applying voltage to G, one can control ID.

More about terminals

All FETs have source, drain, and gate terminals that correspond roughly to the emitter, collector, and base of BJTs. Most FETs have a fourth terminal called the body, base, bulk, or substrate. This fourth terminal serves to bias the transistor into operation; it is rare to make non-trivial use of the body terminal in circuit designs, but its presence is important when setting up the physical layout of an integrated circuit. The size of the gate, length L in the diagram, is the distance between source and drain. The width is the extension of the transistor, in the direction perpendicular to the cross section in the diagram. Typically the width is much larger than the length of the gate. A gate length of 1 µm limits the upper frequency to about 5 GHz, 0.2 µm to about 30 GHz.

The names of the terminals refer to their functions. The gate terminal may be thought of as controlling the opening and closing of a physical gate. This gate permits electrons to flow through or blocks their passage by creating or eliminating a channel between the source and drain. Electrons flow from the source terminal towards the drain terminal if influenced by an applied voltage. The body simply refers to the bulk of the semiconductor in which the gate, source and drain lie. Usually the body terminal is connected to the highest or lowest voltage within the circuit, depending on the type of the FET. The body terminal and the source terminal are sometimes connected together since the source is often connected to the highest or lowest voltage within the circuit, although there are several uses of FETs which do not have such a configuration, such as transmission gates and cascode circuits.

FET operation

The FET controls the flow of electrons (or electron holes) from the source to drain by affecting the size and shape of a "conductive channel" created and influenced by voltage (or lack of voltage) applied across the gate and source terminals. (For simplicity, this discussion assumes that the body and source are connected.) This conductive channel is the "stream" through which electrons flow from source to drain.

In a n-channel depletion-mode device, a negative gate-to-source voltage causes a depletion region to expand in width and encroach on the channel from the sides, narrowing the channel. If the depletion region expands to completely close the channel, the resistance of the channel from source to drain becomes large, and the FET is effectively turned off like a switch. This is called pinch-off, and the voltage at which it occurs is called the pinch-off voltage. Conversely, a positive gate-to-source voltage increases the channel size and allows electrons to flow easily.

In an n-channel enhancement-mode device, a conductive channel does not exist naturally within the transistor, and a positive gate-to-source voltage is necessary to create one. The positive voltage attracts free-floating electrons within the body towards the gate, forming a conductive channel. But first, enough electrons must be attracted near the gate to counter the dopant ions added to the body of the FET; this forms a region with no mobile carriers called a depletion region, and the voltage at which this occurs is referred to as the threshold voltage of the FET. Further gate-to-source voltage increase will attract even more electrons towards the gate which are able to create a conductive channel from source to drain; this process is called inversion.

In a p-channel depletion-mode device, a positive voltage from gate to body creates a depletion layer by forcing the positively charged holes away from the gate-insulator/semiconductor interface, leaving exposed a carrier-free region of immobile, negatively charged acceptor ions.

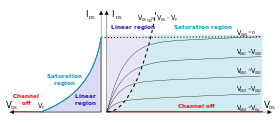

For either enhancement- or depletion-mode devices, at drain-to-source voltages much less than gate-to-source voltages, changing the gate voltage will alter the channel resistance, and drain current will be proportional to drain voltage (referenced to source voltage). In this mode the FET operates like a variable resistor and the FET is said to be operating in a linear mode or ohmic mode.[4][5]

If drain-to-source voltage is increased, this creates a significant asymmetrical change in the shape of the channel due to a gradient of voltage potential from source to drain. The shape of the inversion region becomes "pinched-off" near the drain end of the channel. If drain-to-source voltage is increased further, the pinch-off point of the channel begins to move away from the drain towards the source. The FET is said to be in saturation mode;[6] although some authors refer to it as active mode, for a better analogy with bipolar transistor operating regions.[7][8] The saturation mode, or the region between ohmic and saturation, is used when amplification is needed. The in-between region is sometimes considered to be part of the ohmic or linear region, even where drain current is not approximately linear with drain voltage.

Even though the conductive channel formed by gate-to-source voltage no longer connects source to drain during saturation mode, carriers are not blocked from flowing. Considering again an n-channel enhancement-mode device, a depletion region exists in the p-type body, surrounding the conductive channel and drain and source regions. The electrons which comprise the channel are free to move out of the channel through the depletion region if attracted to the drain by drain-to-source voltage. The depletion region is free of carriers and has a resistance similar to silicon. Any increase of the drain-to-source voltage will increase the distance from drain to the pinch-off point, increasing the resistance of the depletion region in proportion to the drain-to-source voltage applied. This proportional change causes the drain-to-source current to remain relatively fixed, independent of changes to the drain-to-source voltage, quite unlike its ohmic behavior in the linear mode of operation. Thus, in saturation mode, the FET behaves as a constant-current source rather than as a resistor, and can effectively be used as a voltage amplifier. In this case, the gate-to-source voltage determines the level of constant current through the channel.

Composition

The FET can be constructed from a number of semiconductors, with silicon being by far the most common. Most FETs are made with conventional bulk semiconductor processing techniques, using a single crystal semiconductor wafer as the active region, or channel.

Among the more unusual body materials are amorphous silicon, polycrystalline silicon or other amorphous semiconductors in thin-film transistors or organic field-effect transistors (OFETs) that are based on organic semiconductors; often, OFET gate insulators and electrodes are made of organic materials, as well. Such FETs are manufactured using a variety of materials such as silicon carbide (SiC), gallium arsenide (GaAs), gallium nitride (GaN), and indium gallium arsenide (InGaAs). In June 2011, IBM announced that it had successfully used graphene-based FETs in an integrated circuit.[9][10] These transistors are capable of about 2.23 GHz cutoff frequency, much higher than standard silicon FETs.[11]

Types of field-effect transistors

The channel of a FET is doped to produce either an n-type semiconductor or a p-type semiconductor. The drain and source may be doped of opposite type to the channel, in the case of depletion mode FETs, or doped of similar type to the channel as in enhancement mode FETs. Field-effect transistors are also distinguished by the method of insulation between channel and gate. Types of FETs include:

- The JFET (junction field-effect transistor) uses a reverse biased p–n junction to separate the gate from the body.

- The MOSFET (metal–oxide–semiconductor field-effect transistor) utilizes an insulator (typically SiO2) between the gate and the body.

- The DGMOSFET (dual-gate MOSFET) is a FET with two insulated gates.

- The DEPFET is a FET formed in a fully depleted substrate and acts as a sensor, amplifier and memory node at the same time. It can be used as an image (photon) sensor.

- The FREDFET (fast-reverse or fast-recovery epitaxial diode FET) is a specialized FET designed to provide a very fast recovery (turn-off) of the body diode.

- The HIGFET (heterostructure insulated gate field-effect transistor) is now used mainly in research. [1]

- The MODFET (modulation-doped field-effect transistor) uses a quantum well structure formed by graded doping of the active region.

- The TFET (tunnel field-effect transistor) is based on band-to-band tunneling.[12]

- The IGBT (insulated-gate bipolar transistor) is a device for power control. It has a structure akin to a MOSFET coupled with a bipolar-like main conduction channel. These are commonly used for the 200–3000 V drain-to-source voltage range of operation. Power MOSFETs are still the device of choice for drain-to-source voltages of 1 to 200 V.

- The HEMT (high-electron-mobility transistor), also called a HFET (heterostructure FET), can be made using bandgap engineering in a ternary semiconductor such as AlGaAs. The fully depleted wide-band-gap material forms the isolation between gate and body.

- The ISFET (ion-sensitive field-effect transistor) can be used to measure ion concentrations in a solution; when the ion concentration (such as H+, see pH electrode) changes, the current through the transistor will change accordingly.

- The MESFET (metal–semiconductor field-effect transistor) substitutes the p–n junction of the JFET with a Schottky barrier; and is used in GaAs and other III-V semiconductor materials.

- The NOMFET is a nanoparticle organic memory field-effect transistor.[2]

- The GNRFET (graphene nanoribbon field-effect transistor) uses a graphene nanoribbon for its channel.

- The VeSFET (vertical-slit field-effect transistor) is a square-shaped junctionless FET with a narrow slit connecting the source and drain at opposite corners. Two gates occupy the other corners, and control the current through the slit. [3] [4]

- The CNTFET (carbon nanotube field-effect transistor).

- The OFET (organic field-effect transistor) uses an organic semiconductor in its channel.

- The DNAFET (DNA field-effect transistor) is a specialized FET that acts as a biosensor, by using a gate made of single-strand DNA molecules to detect matching DNA strands.

- The QFET (quantum field effect transistor) takes advantage of quantum tunneling to greatly increase the speed of transistor operation by eliminating the traditional transistor's area of electron conduction.

Advantages of FET

The main advantage of the FET is its high input resistance, on the order of 100 MΩ or more. Thus, it is a voltage-controlled device, and shows a high degree of isolation between input and output. It is a unipolar device, depending only on majority current flow.[dubious – discuss]. Because base current noise will increase with shaping time,[13] a FET typically produces less noise than a bipolar junction transistor (BJT), and is thus found in noise sensitive electronics such as tuners and low-noise amplifiers for VHF and satellite receivers. It is relatively immune to radiation. It exhibits no offset voltage at zero drain current and hence makes an excellent signal chopper. It typically has better thermal stability than a BJT.[3]

Disadvantages of FET

It has a relatively low gain-bandwidth product compared to a BJT. The MOSFET has a drawback of being very susceptible to overload voltages, thus requiring special handling during installation.[14] The fragile insulating layer of the MOSFET between the gate and channel makes it vulnerable to electrostatic damage during handling. This is not usually a problem after the device has been installed in a properly designed circuit. watu wa environmental and biosystems had done this assignment...kidenge

Uses of FET

The most commonly used FET is the MOSFET. The CMOS (complementary metal oxide semiconductor) process technology is the basis for modern digital integrated circuits. This process technology uses an arrangement where the (usually "enhancement-mode") p-channel MOSFET and n-channel MOSFET are connected in series such that when one is on, the other is off.

In FETs, electrons can flow in either direction through the channel when operated in the linear mode. The naming convention of drain terminal and source terminal is somewhat arbitrary, as the devices are typically (but not always) built symmetrically from source to drain. This makes FETs suitable for switching analog signals between paths (multiplexing). With this concept, one can construct a solid-state mixing board, for example.

A common use of the FET is as an amplifier. For example, due to its large input resistance and low output resistance, it is effective as a buffer in common-drain (source follower) configuration.

IGBTs see application in switching internal combustion engine ignition coils, where fast switching and voltage blocking capabilities are important.

See also FET

References

- ^ http://www.computerhistory.org/semiconductor/timeline/1960-MOS.html

- ^ Jacob Millman (1985). Electronic devices and circuits. Singapore: McGraw-Hill International. p. 397. ISBN 0-07-085505-6.

- ^ a b Millman (1985). Electronic devices and circuits. Singapore: McGraw-Hill. pp. 384–385. ISBN 0-07-085505-6.

- ^ C Galup-Montoro & Schneider MC (2007). MOSFET modeling for circuit analysis and design. London/Singapore: World Scientific. p. 83. ISBN 981-256-810-7.

- ^ Norbert R Malik (1995). Electronic circuits: analysis, simulation, and design. Englewood Cliffs, NJ: Prentice Hall. pp. 315–316. ISBN 0-02-374910-5.

- ^ RR Spencer & Ghausi MS (2001). Microelectronic circuits. Upper Saddle River NJ: Pearson Education/Prentice-Hall. p. 102. ISBN 0-201-36183-3.

- ^

A. S. Sedra and K.C. Smith (2004). Microelectronic circuits (Fifth Edition ed.). New York: Oxford. p. 552. ISBN 0-19-514251-9.

{{cite book}}:|edition=has extra text (help) - ^

PR Gray, PJ Hurst, SH Lewis & RG Meyer (2001). Analysis and design of analog integrated circuits (Fourth Edition ed.). New York: Wiley. pp. §1.5.2 p. 45. ISBN 0-471-32168-0.

{{cite book}}:|edition=has extra text (help)CS1 maint: multiple names: authors list (link) - ^ http://www.physorg.com/news/2011-06-ibm-graphene-based-circuit.html

- ^ Lin, Y.-M., Valdes-Garcia, A., Han, S.-J., Farmer, D. B., Sun, Y, Wu, Y, Dimitrakopoulos, C., Grill, A, Avouris, P, and Jenkins, K. A. (2011). "Wafer-Scale Graphene Integrated Circuit". Science. 332: 1294–1297. doi:10.1126/science.1204428. PMID 21659599.

{{cite journal}}: CS1 maint: multiple names: authors list (link) - ^ http://physicsworld.com/cws/article/news/2012/dec/10/flexible-graphene-transistor-sets-new-records

- ^ Attention: This template ({{cite doi}}) is deprecated. To cite the publication identified by doi:10.1038/nature10679, please use {{cite journal}} (if it was published in a bona fide academic journal, otherwise {{cite report}} with

|doi=10.1038/nature10679instead. - ^ http://www-physics.lbl.gov/~spieler/physics_198_notes/PDF/VIII-5-noise.pdf

- ^ Allen Mottershead (2004). Electronic devices and circuits. New Delhi: Prentice-Hall of India. ISBN 81-203-0124-2.

External links

- Field Effect Transistor Applications

- PBS The Field Effect Transistor

- Junction Field Effect Transistor

- CMOS gate circuitry

- Winning the Battle Against Latchup in CMOS Analog Switches

- Nanotube FETs at IBM Research

- Field Effect Transistors in Theory and Practice

- The Field Effect Transistor as a Voltage Controlled Resistor