AMD K6

This article has multiple issues. Please help improve it or discuss these issues on the talk page. (Learn how and when to remove these messages)

|

| |

| General information | |

|---|---|

| Launched | April 2, 1997 |

| Discontinued | May 28, 1998 |

| Common manufacturer | |

| Performance | |

| Max. CPU clock rate | 166 MHz to 300 MHz |

| FSB speeds | 66 MHz |

| Architecture and classification | |

| Technology node | 350 nm to 250 nm |

| Microarchitecture | x86 |

| Instruction set | MMX |

| Physical specifications | |

| Cores |

|

| Socket | |

| Products, models, variants | |

| Core names |

|

| History | |

| Predecessor | K5 |

| Successor | K6-2 |

The K6 microprocessor was launched by AMD in 1997. The main advantage of this particular microprocessor is that it was designed to fit into existing desktop designs for Pentium-branded CPUs. It was marketed as a product that could perform as well as its Intel Pentium II equivalent but at a significantly lower price. The K6 had a considerable impact on the PC market and presented Intel with serious competition.

Background

The AMD K6 is a superscalar P5 Pentium-class microprocessor, manufactured by AMD, which superseded the K5.

The AMD K6 is based on the Nx686 microprocessor that NexGen was designing when it was acquired by AMD. Despite the name implying a design evolving from the K5, it is in fact a totally different design that was created by the NexGen team, including chief processor architect Greg Favor,[1][2] and adapted after the AMD purchase. The K6 processor included a feedback dynamic instruction reordering mechanism, MMX instructions, and a floating-point unit (FPU). It was also made pin-compatible with Intel's Pentium, enabling it to be used in the widely available "Socket 7"-based motherboards. Like the AMD K5, Nx586, and Nx686 before it, the K6 translated x86 instructions on the fly into dynamic buffered sequences of micro-operations. A later variation of the K6 CPU, K6-2, added floating-point-based SIMD instructions, called 3DNow!.

The K6 was originally launched in April 1997, running at speeds of 166 and 200 MHz. It was followed by a 233 MHz version later in 1997. Initially, the AMD K6 processors used a Pentium II-based performance rating (PR2) to designate their speed.[3] The PR2 rating was dropped because the rated frequency of the processor was the same as the real frequency. The release of the 266 MHz version of this chip was not until the second quarter of 1998, when AMD was able to move to the 0.25-micrometre manufacturing process. The lower voltage and higher multiplier of the K6-266 meant that it was not fully compatible with some Socket 7 motherboards, similar to the later K6-2 processors. The final iteration of the K6 design was released in May 1998, running at 300 MHz.

-

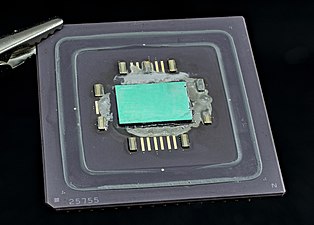

A delidded AMD K6 processor

-

Die shot of an AMD K6-233APR processor

Features

Bobit:

- Seven execution units specialized in parallelized instructions[4]

- x86 Decoders that translate x86 Assembly to RISC86 instructions[5] [failed verification]

- IEEE 1149.1 Boundary Scan

- Speculative execution optimization

- Out of Order execution

- Register Renaming

Models

K6 (Model 6)

- 8.8 million transistors in 350 nm

- L1-Cache: 32 + 32 KB (data + instructions)

- MMX

- Socket 7

- Front side bus: 66 MHz

- First release: April 2, 1997

- VCore: 2.9 V (166/200) 3.2/3.3 V (233)

- Clockrate: 166, 200, 233 MHz

K6 "Little Foot" (Model 7)

- CPUID: family 5, model 7, stepping 0

- 8.8 million transistors in 250 nm

- L1-Cache: 32 + 32 KB (data + instructions)

- MMX

- Socket 7

- Front side bus: 66 MHz

- First release: January 6, 1998

- VCore: 2.2 V

- Clockrate: 200, 233, 266, 300 MHz

Successor

The K6 line was updated with SIMD instructions (Branded as AMD 3DNow!) to create the K6-2 line of microprocessors.

References

- ^ p. 48, "AMD 3DNow! technology: architecture and implementations", S. Oberman, G. Favor, and F. Weber, IEEE Micro 19, #2 (March/April 1999), pp. 37–48, doi:10.1109/40.755466.

- ^ Who are the Computer Architects?, Mark Smotherman, Clemson University, updated June 9, 2010.

- ^ Shimpi, Anand Lal (3 April 1997). "AMD K6 Review". AnandTech. Retrieved 14 September 2022.

- ^ "AMD-K6 Processor Data Sheet" (PDF). AMD. March 1998.

- ^ "The legend of "x86 CPUs decode instructions into RISC form internally" - Fanael's random ruminations". fanael.github.io. Retrieved 2023-06-01.

Further reading

- Gwennap, Linley (31 March 1997). "K6 Is World's Fastest x86 Chip". Microprocessor Report.

- Slater, Michael (28 October 1998). "K6 to Boost AMD's Position in 1997". Microprocessor Report.

External links

- "AMD: AMD-K6 Processor". Archived from the original on February 24, 2008. Retrieved March 26, 2005.

- AMD K6, first of an impressive dynasty

- Technical overview of the AMD-K6 series

- technical dissection of the 6th generation x86 CPUs