Zilog Z80

A Z80 manufactured in June 1976 according to the date stamp | |

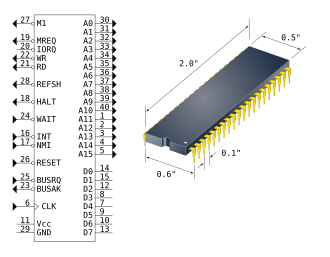

| General information | |

|---|---|

| Launched | March 1976 |

| Common manufacturer | |

| Performance | |

| Max. CPU clock rate | 2.5, 4, 6, 8 MHz to 10 MHz with CMOS variant up to 20 MHz and binary compatible derivatives (from Zilog) up to 33 and 50 MHz. |

The Z80 is an 8-bit microprocessor introduced by Zilog as the startup company's first product. The Z80 was conceived by Federico Faggin in late 1974 and developed by him and his 11 employees starting in early 1975. The first working samples were delivered in March 1976, and it was officially introduced on the market in July 1976. With the revenue from the Z80, the company built its own chip factories and grew to over a thousand employees over the following two years.[2]

The Zilog Z80 is a software-compatible extension and enhancement of the Intel 8080 and, like it, was mainly aimed at embedded systems. Although used in that role, the Z80 also became one of the most widely used CPUs in desktop computers and home computers from the 1970s to the mid-1980s.[3][4] It was also common in military applications, musical equipment such as synthesizers (like the Roland Jupiter-8), and coin operated arcade games of the late 1970s and early 1980s including Pac-Man.

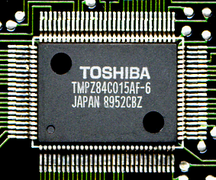

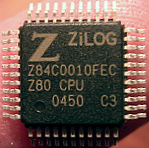

Zilog licensed the Z80 to the US-based Synertek and Mostek, which had helped them with initial production, as well as to a European second source manufacturer, SGS. The design was also copied by several Japanese, East European and Soviet manufacturers.[i] This won the Z80 acceptance in the world market since large companies like NEC, Toshiba, Sharp, and Hitachi started to manufacture the device (or their own Z80-compatible clones or designs).

In recent decades Zilog has refocused on the ever-growing market for embedded systems and the most recent Z80-compatible microcontroller family, the fully pipelined 24-bit eZ80 with a linear 16 MB address range, has been successfully introduced alongside the simpler Z80 and Z180 products.

History

The Z80 came about when physicist Federico Faggin left Intel at the end of 1974 to found Zilog with Ralph Ungermann. At Fairchild Semiconductor, and later at Intel, Faggin had been working on fundamental transistor and semiconductor manufacturing technology. He also developed the basic design methodology used for memories and microprocessors at Intel and led the work on the Intel 4004, the 8080 and several other ICs. Masatoshi Shima, the principal logic and transistor level-designer of the 4004 and the 8080 under Faggin's supervision, joined the Zilog team.

According to the designers, the primary targets for the Z80 CPU (and its optional support and peripheral ICs[ii]) were products like intelligent terminals, high end printers and advanced cash registers as well as telecom equipment, industrial robots and other kinds of automation equipment.

By March 1976, Zilog had developed the Z80 as well as an accompanying assembler based development system for its customers, and by July 1976, this was formally launched onto the market.[5] Some of the Z80 support and peripheral ICs were under development at this point, and many of them were launched during the following year.

Early Z80s were manufactured by Synertek and Mostek, before Zilog had its own manufacturing factory ready, in late 1976. These companies were chosen because they could do the ion implantation needed to create the depletion-mode MOSFETs that the Z80 design used as load transistors in order to cope with a single 5 Volt power supply.[iii]

Faggin designed the instruction set to be binary compatible with the Intel 8080[6][7] so that most 8080 code, notably the CP/M operating system and Intel's PL/M compiler for 8080 (as well as its generated code), would run unmodified on the new Z80 CPU. Masatoshi Shima designed most of the microarchitecture as well as the gate and transistor levels of the Z80 CPU, assisted by a small number of engineers and layout people.[8][9] CEO Federico Faggin was actually heavily involved in the chip layout work, together with two dedicated layout people. According to Faggin, he worked 80 hours a week in order to meet the tight schedule given by the financial investors.[10]

The Z80 offered many improvements over the 8080:[7]

- An enhanced instruction set[11] including single-bit addressing, shifts/rotates on memory and registers other than the accumulator, rotate instructions for BCD number strings in memory, program looping, program counter relative jumps, block copy, block input/output (I/O), and byte search instructions.[12] The Z80 incorporated an overflow flag and had better support for signed 8- and 16-bit arithmetics.[iv]

- New IX and IY index registers with instructions for direct base+offset addressing

- A better interrupt system

- A more automatic and general vectorized interrupt system, mode 2, primarily intended for Zilog's line of counter/timers, DMA and communications controllers, as well as a fixed vector interrupt system, mode 1, for simple systems with minimal hardware (with mode 0 being the 8080-compatible mode).[13]

- A non maskable interrupt (NMI) which can be used to respond to power down situations or other high priority events (and allowing a minimalistic Z80 system to easily implement a two-level interrupt scheme in mode 1).

- Two separate register files, which could be quickly switched, to speed up response to interrupts such as fast asynchronous event handlers or a multitasking dispatcher. Although they were not intended as extra registers for general code, they were nevertheless used that way in some applications.[v]

- Less hardware required for power supply, clock generation and interface to memory and I/O

- Single 5-volt power supply (the 8080 needed -5 V/+5 V/+12 V).

- Single-phase 5-volt clock (the 8080 needed a high-amplitude (9 to 12 volt) non-overlapping two-phase clock).

- A built-in DRAM refresh mechanism that would otherwise have to be provided by external circuitry.[vi]

- Non-multiplexed buses (the 8080 had state-signals multiplexed onto the data bus).

- A special reset function which clears only the program counter so that a single Z80 CPU could be used in a development system such as an in-circuit emulator.[14]

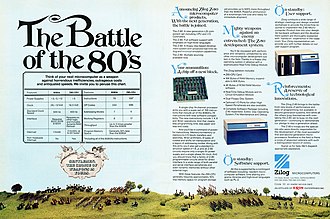

The Z80 took over from the 8080 and its offspring, the 8085, in the processor market,[15] and became one of the most popular 8-bit CPUs.[3][4] Zilog was later by a few years than Intel (with its 80C85) to produce a low-power CMOS CPU, and this resulted in the Intel chip first appearing in use with battery-powered portable computers, such as Tandy/Radio Shack's TRS-80 Model 100 laptop from April 1983. In following years, however, the CMOS Z80 would dominate this market.

Some organizations, such as British Telecom, remained loyal to the 8085 for embedded applications owing to their familiarity with it, and to its on-chip support for a serial interface and multi-level interrupt architecture. Perhaps a key to the initial success of the Z80 was the built-in DRAM refresh, and other features which allowed systems to be built with fewer support chips (Z80 embedded systems typically use static RAM and hence do not need this refresh).

For the original NMOS design, the specified upper clock frequency limit increased successively from the introductory 2.5 MHz, via the well known 4 MHz (Z80A), up to 6 (Z80B) and 8 MHz (Z80H).[16][17] The NMOS version has been produced as a 10 MHz part since the late 1980s. CMOS versions were developed with specified upper frequency limits ranging from 4 MHz up to 20 MHz for the version sold today. The CMOS versions allowed low-power sleep with internal state retained, having no lower frequency limit.[vii] The fully compatible derivatives HD64180/Z180[18][19] and eZ80 are currently specified for up to 33 and 50 MHz respectively.

Design

Programming model and register set

The programming model and register set of the Z80 are fairly conventional, ultimately based on the register structure of the Datapoint 2200. The Z80 was designed as an extension of the Intel 8080, created by the same engineers, which in turn was an extension of the 8008. The 8008 was basically a PMOS implementation of the TTL-based CPU of the Datapoint 2200.[viii]

The 2200 design allowed 8-bit registers H and L (High and Low) to be paired into a 16-bit address register HL.[ix] In the 8080, this pairing was added to the BC and DE pairs as well, while HL was generalized to allow use as a 16-bit accumulator, not just an address register. The 8080 also introduced the important 8-bit immediate data mode for accumulator operations, and immediate 16-bit data for HL, BC and DE loads. Furthermore, direct 16-bit copying between HL and memory was now possible, using a direct address.

The Z80 orthogonalized this further by making all 16-bit register pairs, including IX and IY, more general purpose, as well as allowing 16-bit copying directly to and from memory for all of these pairs. The 16-bit IX and IY registers in the Z80 are primarily intended as base address-registers, where a particular instruction supplies a constant offset that is added to the previous values, but they are also usable as 16-bit accumulators, among other things. The Z80 also introduced a new signed overflow flag and complemented the fairly simple 16-bit arithmetics of the 8080 with dedicated instructions for signed 16-bit arithmetics.

The 8080-compatible registers AF, BC, DE, HL are duplicated as two separate banks in the Z80,[21] where the processor can quickly switch from one bank to the other;[22] a feature useful for speeding up responses to single-level, high-priority interrupts. A similar feature was present in the 2200, but was never implemented at Intel. The dual register-set is very useful in the embedded role, as it improves interrupt handling performance, but found widespread use in the personal computer role as an additional set of general registers for complex code like floating point arithmetics or home computer games.

Registers

| The Z80 registers | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

As on the 8080, 8-bit registers are typically paired to provide 16-bit versions. The 8080 compatible registers[23] are:

AF: 8-bit accumulator (A) and flag bits (F) carry, zero, minus, parity/overflow, half-carry (used for BCD), and an Add/Subtract flag (usually called N) also for BCDBC: 16-bit data/address register or two 8-bit registersDE: 16-bit data/address register or two 8-bit registersHL: 16-bit accumulator/address register or two 8-bit registersSP: stack pointer, 16 bitsPC: program counter, 16 bits

The new registers introduced with the Z80 are:

IX: 16-bit index or base register for 8-bit immediate offsetsIY: 16-bit index or base register for 8-bit immediate offsetsI: interrupt vector base register, 8 bitsR: DRAM refresh counter, 8 bits (msb does not count)AF': alternate (or shadow) accumulator and flags (toggled in and out with EX AF,AF' )BC',DE'andHL': alternate (or shadow) registers (toggled in and out with EXX)- Four bits of interrupt status and interrupt mode status

There is no direct access to the alternate registers; instead, two special instructions, EX AF,AF' and EXX,[23] each toggles one of two multiplexer flip-flops. This enables fast context switches for interrupt service routines: EX AF, AF' may be used alone, for really simple and fast interrupt routines, or together with EXX to swap the whole BC, DE, HL set. This is still several times as fast as pushing the same registers on the stack. Slower, lower priority, or multi level interrupts normally use the stack to store registers, however.

The refresh register, R, increments each time the CPU fetches an opcode (or opcode prefix) and has no simple relationship with program execution. This has sometimes been used to generate pseudorandom numbers in games, and also in software protection schemes.[citation needed] It has also been employed as a "hardware" counter in some designs; an example of this is the ZX81, which lets it keep track of character positions on the TV screen by triggering an interrupt at wrap around (by connecting INT to A6).

The interrupt vector register, I, is used for the Z80 specific mode 2 interrupts (selected by the IM 2 instruction). It supplies the high byte of the base address for a 128-entry table of service routine addresses which are selected via an index sent to the CPU during an interrupt acknowledge cycle; this index is simply the low byte part of the pointer to the tabulated indirect address pointing to the service routine.[13] The pointer identifies a particular peripheral chip or peripheral function or event, where the chips are normally connected in a so-called daisy chain for priority resolution. Like the refresh register, this register has also sometimes been used creatively; in interrupt modes 0 and 1 (or in a system not using interrupts) it can be used as simply another 8-bit data register.

The instructions LD A,R and LD A,I affect the Z80 flags register, unlike all the other LD (load) instructions. The Sign (bit 7) and Zero (bit 6) flags are set according to the data loaded from the Refresh or Interrupt source registers. For both instructions, the Parity/Overflow flag (bit 2) is set according to the current state of the IFF2 flip-flop.[24]

Z80 assembly language

Datapoint 2200 and Intel 8008

The first Intel 8008 assembly language was based on a very simple (but systematic) syntax inherited from the Datapoint 2200 design. This original syntax was later transformed into a new, somewhat more traditional, assembly language form for this same original 8008 chip. At about the same time, the new assembly language was also extended to accommodate the added addressing possibilities in the more advanced Intel 8080 chip (the 8008 and 8080 shared a language subset without being binary compatible; however, the 8008 was binary compatible with the Datapoint 2200).

In this process, the mnemonic L, for LOAD, was replaced by various abbreviations of the words LOAD, STORE and MOVE, intermixed with other symbolic letters. The mnemonic letter M, for memory (referenced by HL), was lifted out from within the instruction mnemonic to become a syntactically freestanding operand, while registers and combinations of registers became very inconsistently denoted; either by abbreviated operands (MVI D, LXI H and so on), within the instruction mnemonic itself (LDA, LHLD and so on), or both at the same time (LDAX B, STAX D and so on).

| Intel 8008 Datapoint 2200 |

Intel 8080 Intel 8085 |

Zilog Z80 | Intel 8086/ Intel 8088 |

|---|---|---|---|

| before ca. 1973 | ca. 1974 | 1976 | 1978 |

LBC

|

MOV B,C

|

LD B,C

|

MOV BL,CL

|

--

|

LDAX B

|

LD A,(BC)

|

MOV AL,[BX]

|

LAM

|

MOV A,M

|

LD A,(HL)

|

MOV AL,[BP]

|

LBM

|

MOV B,M

|

LD B,(HL)

|

MOV BL,[BP]

|

--

|

STAX D

|

LD (DE),A

|

MOV [DX],AL[x]

|

LMA

|

MOV M,A

|

LD (HL),A

|

MOV [BP],AL

|

LMC

|

MOV M,C

|

LD (HL),C

|

MOV [BP],CL

|

LDI 56

|

MVI D,56

|

LD D,56

|

MOV DL,56

|

LMI 56

|

MVI M,56

|

LD (HL),56

|

MOV byte ptr [BP],56

|

--

|

LDA 1234

|

LD A,(1234)

|

MOV AL,[1234]

|

--

|

STA 1234

|

LD (1234),A

|

MOV [1234],AL

|

--

|

--

|

LD B,(IX+56)

|

MOV BL,[SI+56]

|

--

|

--

|

LD (IX+56),C

|

MOV [SI+56],CL

|

--

|

--

|

LD (IY+56),78

|

MOV byte ptr [DI+56],78

|

--

|

LXI B,1234

|

LD BC,1234

|

MOV BX,1234

|

--

|

LXI H,1234

|

LD HL,1234

|

MOV BP,1234

|

--

|

SHLD 1234

|

LD (1234),HL

|

MOV [1234],BP

|

--

|

LHLD 1234

|

LD HL,(1234)

|

MOV BP,[1234]

|

--

|

--

|

LD BC,(1234)

|

MOV BX,[1234]

|

--

|

--

|

LD IX,(1234)

|

MOV SI,[1234]

|

Illustration of four syntaxes, using samples of equivalent, or (for 8086) very similar, load and store instructions.[25] The Z80 syntax uses parentheses around an expression to indicate that the value should be used as a memory address (as mentioned below), while the 8086 syntax uses brackets instead of ordinary parentheses for this purpose. Both Z80 and 8086 use the + sign to indicate that a constant is added to a base register to form an address

New syntax

Because Intel claimed a copyright on their assembly mnemonics,[26] a new assembly syntax had to be developed for the Z80. This time a more systematic approach was used:

- All registers and register pairs are explicitly denoted by their full names

- Parentheses are consistently used to indicate "memory contents at" (constant address or variable pointer dereferencing) with the exception of some jump instructions.[27]

- All load and store instructions use the same mnemonic name, LD, for LOAD (a return to the simplistic Datapoint 2200 vocabulary); other common instructions, such as ADD and INC, use the same mnemonic regardless of addressing mode or operand size. This is possible because the operands themselves carry enough information.

These principles made it straightforward to find names and forms for all new Z80 instructions, as well as orthogonalizations of old ones, such as LD BC,(1234).

Apart from naming differences, and despite a certain discrepancy in basic register structure, the Z80 and 8086 syntax are virtually isomorphic for a large portion of instructions. Only quite superficial similarities (such as the word MOV, or the letter X, for extended register) exist between the 8080 and 8086 assembly languages, although 8080 programs can be translated to 8086 assembly language by translator programs.[28][29]

Instruction set and encoding

The Z80 uses 252 out of the available 256 codes as single byte opcodes ("root instruction"); the four remaining codes are used extensively as opcode prefixes:[30] CB and ED enable extra instructions and DD or FD selects IX+d or IY+d respectively (in some cases without displacement d) in place of HL. This scheme gives the Z80 a large number of permutations of instructions and registers; Zilog categorizes these into 158 different "instruction types", 78 of which are the same as those of the Intel 8080[30] (allowing operation of most 8080 programs on a Z80). The Zilog documentation further groups instructions into the following categories:

- 8-bit arithmetic and logic operations

- 16-bit arithmetic

- 8-bit load

- 16-bit load

- Bit set, reset, and test

- Call, return, and restart

- Exchange, block transfer, and search

- General purpose arithmetic and CPU control

- Input and output

- Jump

- Rotate and shift

No multiply instructions are available in the original Z80.[31] Different sizes and variants of additions, shifts, and rotates have somewhat differing effects on flags because most of the flag-changing properties of the 8080 were copied. However, the parity flag bit P of the 8080 (bit 2) is called P/V (parity/overflow) in the Z80 as it serves the additional purpose of a twos complement overflow indicator, a lacking feature in the 8080. Arithmetic instructions on the Z80 set it to indicate overflow rather than parity, while bitwise instructions still use it as a parity flag. This new overflow flag is used for all new Z80-specific 16-bit operations (ADC, SBC) as well as for 8-bit arithmetic operations, although the 16-bit operations inherited from the 8080 (ADD, INC, DEC) do not affect it. Also, bit 1 of the flags register (a spare bit on the 8080) is used as a flag, N, that indicates whether the last arithmetic instruction executed was a subtraction or addition. The Z80 version of the DAA instruction (Decimal Adjust Accumulator for BCD arithmetic) checks the N flag and behaves accordingly, so a (hypothetical) subtraction followed later by DAA will yield a different result on an old 8080 than on the Z80. However, this would likely be erroneous code on the 8080, as DAA was defined for addition only on that processor.

The Z80 has six new LD instructions that can load the DE, BC, and SP register pairs from memory, and load memory from these three register pairs—unlike the 8080.[32] As on the 8080, load instructions do not affect the flags (except for the special purpose I and R register loads). A result of a regular encoding (common with the 8080) is that each of the 8-bit registers can be loaded from themselves (e.g. LD A,A). This is effectively a NOP.

New block transfer instructions can move up to 64 kilobytes from memory to memory or between memory and I/O peripheral ports. Block instructions LDIR and LDDR (LoaD,Increment/Decrement,Repeat) use HL to point to the source address, DE to the destination address, and BC as a byte counter. Bytes are copied from source to destination, the pointers are incremented or decremented, and the byte counter is decremented until BC reaches zero. Non-repeating versions LDI and LDD move a single byte and bump the pointers and byte counter, which if becomes zero resets the P/V flag. Corresponding memory-to-I/O instructions INIR, INDR, OTIR, OTDR, INI, IND, OUTI and OUTD operate similarly. The Z80 can input and output any register to an I/O port using register C to designate the port (the 8080 only performs I/O through the accumulator A).

The last group of block instructions perform a CP compare operation between the byte at (HL) and the accumulator A. Register pair DE is not used. The repeating versions CPIR and CPDR only terminate if BC goes to zero or a match is found. HL is left pointing to the byte after (CPIR) or before (CPDR) the matching byte. If no match is found the Z flag is reset. There are non-repeating versions CPI and CPD.

Unlike the 8080, the Z80 can jump to a relative address (JR instead of JP) using a signed 8-bit displacement. Only the Zero and Carry flags can be tested for these new two-byte JR instructions. A two-byte instruction specialized for program looping is also new to the Z80. DJNZ (Decrement Jump if Non-Zero) takes a signed 8-bit displacement as an immediate operand. The B register is decremented. If the result is nonzero then program execution jumps relative to the address of the PC plus the displacement. The flags remain unaltered. To perform an equivalent loop on an 8080 would require separate decrement and jump (to a two-byte absolute address) instructions, and the flag register would be altered.

The index register (IX/IY, often abbreviated XY) instructions can be useful for accessing data organised in fixed heterogenous structures (such as records) or at fixed offsets relative a variable base address (as in recursive stack frames) and can also reduce code size by removing the need for multiple short instructions using non-indexed registers. However, although they may save speed in some contexts when compared to long/complex "equivalent" sequences of simpler operations, they incur a lot of additional CPU time (e.g. 19 T-states to access one indexed memory location vs. as little as 11 to access the same memory using HL and INC to point to the next). Thus, for simple or linear accesses of data, use of IX and IY tend to be slower and occupy more memory. Still, they may be useful in cases where the 'main' registers are all occupied, by removing the need to save/restore registers. Their officially undocumented 8-bit halves (see below) can be especially useful in this context, for they incur less slowdown than their 16-bit parents. Similarly, instructions for 16-bit additions are not particularly fast (11 clocks) in the original Z80; nonetheless, they are about twice as fast as performing the same calculations using 8-bit operations, and equally important, they reduce register usage. It was not uncommon for programmers to "poke" different (typically calculated dynamically) offset displacement bytes into indexed instructions; this is an example of self-modifying code which was regular practice on nearly all early 8-bit processors with non-pipelined execution units.

The index registers have a parallel instruction to JP (HL), which is JP (XY). This is often seen in stack-oriented languages like Forth which at the end of every Forth word (atomic subroutines comprising the language) must jump unconditionally back to their thread interpreter routines. Typically this jump instruction appears many hundreds of times in an application, and using JP (XY) rather than JP THREAD saves a byte and two t-states each occurrence. This naturally makes the index register unavailable for any other use, or else the need to constantly reload it would negate its efficiency.

The 10-year-newer microcoded Z180 design could initially afford more "chip area", permitting a slightly more efficient implementation (using a wider ALU, among other things); similar things can be said for the Z800, Z280, and Z380. However, it was not until the fully pipelined eZ80 was launched in 2001 that those instructions finally became approximately as cycle-efficient as it is technically possible to make them, i.e. given the Z80 encodings combined with the capability to do an 8-bit read or write every clock cycle.[citation needed]

Undocumented instructions

The index registers, IX and IY, were intended as flexible 16 bit pointers, enhancing the ability to manipulate memory, stack frames and data structures. Officially, they were treated as 16-bit only. In reality they were implemented as a pair of 8-bit registers,[33] in the same fashion as the HL register, which is accessible either as 16 bits or separately as the High and Low registers. The binary opcodes (machine language) were identical, but preceded by a new opcode prefix.[34] Zilog published the opcodes and related mnemonics for the intended functions, but did not document the fact that every opcode that allowed manipulation of the H and L registers was equally valid for the 8 bit portions of the IX and IY registers. For example, the opcode 26h followed by an immediate byte value (LD H,n) will load that value into the H register. Preceding this two-byte instruction with the IX register's opcode prefix, DD, would instead result in the most significant 8 bits of the IX register being loaded with that same value. A notable exception to this would be instructions similar to LD H,(IX+d) which make use of both the HL and IX or IY registers in the same instruction;[34] in this case the DD prefix is only applied to the (IX+d) portion of the instruction. The halves of the XY registers could also hold operands for 8-bit arithmetic, logical and compare instructions, sparing the regular 8-bit registers for other use. The undocumented ability to increment and decrement the upper half of an index register made it easy to expand the range of the normal indexed instructions, without having to resort to the legal ADD/SBC XY,DE or ADD/SBC XY,BC.

There are several other undocumented instructions as well.[35] Undocumented or illegal opcodes are not detected by the Z80 and have various effects, some of which are useful. However, as they are not part of the formal definition of the instruction set, different implementations of the Z80 are not guaranteed to work the same way for every undocumented opcode.

Bugs

The OTDR instruction does not conform to the Z80 documentation. Both the OTDR and OTIR instructions are supposed to leave the carry (C) flag unmodified. The OTIR instruction operates correctly; however, during the execution of the OTDR instruction, the carry flag takes the results of a spurious compare between the accumulator (A) and the last output of the OTDR instruction.

Example code

The following Z80 assembly language source code is for a subroutine named memcpy that copies a block of data bytes of a given size from one location to another. Important: the example code does not handle a certain case where the destination block overlaps the source; a fatal bug. The sample code is extremely inefficient, intended to illustrate various instruction types, rather than best practices for speed. In particular, the Z80 has a single instruction that will execute the entire loop (LDIR). The data block is copied one byte at a time, and the data movement and looping logic utilizes 16-bit operations. Note that the assembled code is binary-compatible with the Intel 8080 and 8085 CPUs.

1000

1000

1000 78

1001 B1

1002 C8

1003 1A

1004 77

1005 13

1006 23

1007 0B

1008 C3 00 10

100B

|

; memcpy --

; Copy a block of memory from one location to another.

;

; Entry registers

; BC - Number of bytes to copy

; DE - Address of source data block

; HL - Address of target data block

;

; Return registers

; BC - Zero

org 1000h ;Origin at 1000h

memcpy public

loop ld a,b ;Test BC,

or c ;If BC = 0,

ret z ;Return

ld a,(de) ;Load A from (DE)

ld (hl),a ;Store A into (HL)

inc de ;Increment DE

inc hl ;Increment HL

dec bc ;Decrement BC

jp loop ;Repeat the loop

end

|

Instruction execution

Each instruction is executed in steps that are usually termed machine cycles (M-cycles), each of which can take between three and six clock periods (T-cycles).[36] Each M-cycle corresponds roughly to one memory access or internal operation. Many instructions actually end during the M1 of the next instruction which is known as a fetch/execute overlap.

| Total

M-cycles |

instruction | M1 | M2 | M3 | M4 | M5 | M6 |

|---|---|---|---|---|---|---|---|

| 1[37] | INC BC

|

opcode | |||||

| 2[38] | ADD A,n

|

opcode | n | ||||

| 3[39] | ADD HL,DE

|

opcode | internal | internal | |||

| 4[40] | SET b,(HL)

|

prefix | opcode | R(HL), set | W(HL) | ||

| 5[41] | LD (IX+d),n

|

prefix | opcode | d | n,add | W(IX+d) | |

| 6[42] | INC (IY+d)

|

prefix | opcode | d | add | R(IY+d),inc | W(IY+d) |

The Z80 machine cycles are sequenced by an internal state machine which builds each M-cycle out of 3, 4, 5 or 6 T-cycles depending on context. This avoids cumbersome asynchronous logic and makes the control signals behave consistently at a wide range of clock frequencies. It also means that a higher frequency crystal must be used than without this subdivision of machine cycles (approximately 2–3 times higher). It does not imply tighter requirements on memory access times, since a high resolution clock allows more precise control of memory timings and so memory can be active in parallel with the CPU to a greater extent, allowing more efficient use of available memory bandwidth.[citation needed]

One central example of this is that, for opcode fetch, the Z80 combines two full clock cycles into a memory access period (the M1-signal). In the Z80 this signal lasts for a relatively larger part of the typical instruction execution time than in a design such as the 6800, 6502, or similar, where this period would typically last typically 30-40% of a clock cycle.[citation needed] With memory chip affordability (i.e. access times around 450-250 ns in the 1980s[citation needed]) typically determining the fastest possible access time, this meant that such designs were locked to a significantly longer clock cycle (i.e. lower internal clock speed) than the Z80.

Memory was generally slow compared to the state machine sub-cycles (clock cycles) used in contemporary microprocessors. The shortest machine cycle that could safely be used in embedded designs has therefore often been limited by memory access times, not by the maximum CPU frequency (especially so during the home computer era). However, this relation has slowly changed during the last decades, particularly regarding SRAM; cacheless, single-cycle designs such as the eZ80 have therefore become much more meaningful recently.

The content of the refresh register R is sent out on the lower half of the address bus along with a refresh control signal while the CPU is decoding and executing the fetched instruction. During refresh the contents of the Interrupt register I are sent out on the upper half of the address bus.[43]

Compatible peripherals

Zilog introduced a number of peripheral parts for the Z80, which all support the Z80's interrupt handling system and I/O address space. These include the Counter/Timer Channel (CTC),[44] the SIO (Serial Input Output), the DMA (Direct Memory Access), the PIO (Parallel Input-Output) and the DART (Dual Asynchronous Receiver Transmitter). As the product line developed, low-power, high-speed and CMOS versions of these chips were introduced.

-

PIO Z84C2008

-

CTC Z84C3008

-

SIO Z84C4008

Like the 8080, 8085 and 8086 processors, but unlike processors such as the Motorola 6800 and MOS Technology 6502, the Z80 and 8080 has a separate control line and address space for I/O instructions. While some Z80-based computers such as the Osborne 1 used "Motorola-style" memory mapped input/output devices, usually the I/O space was used to address one of the many Zilog peripheral chips compatible with the Z80. Zilog I/O chips supported the Z80's new mode 2 interrupts which simplified interrupt handling for large numbers of peripherals.

The Z80 was officially described as supporting 16-bit (64 KB) memory addressing, and 8-bit (256 ports) I/O-addressing. All I/O instructions actually assert the entire 16-bit address bus. OUT (C),reg and IN reg,(C) places the contents of the entire 16 bit BC register on the address bus;[45] OUT (n),A and IN A,(n) places the contents of the A register on b8-b15 of the address bus and n on b0-b7 of the address bus. A designer could choose to decode the entire 16 bit address bus on I/O operations in order to take advantage of this feature, or use the high half of the address bus to select subfeatures of the I/O device. This feature has also been used to minimise decoding hardware requirements, such as in the Amstrad CPC/PCW and ZX81.

Second sources and derivatives

Second sources

Mostek, who produced the first Z80 for Zilog, offered it as second-source as MK3880. SGS-Thomson (now STMicroelectronics) was a second-source, too, with their Z8400. Sharp and NEC developed second sources for the NMOS Z80, the LH0080 and µPD780C, respectively. The LH0080 was used in various home computers and personal computers made by Sharp and other Japanese manufacturers, including Sony MSX computers, and a number of computers in the Sharp MZ series.[46]

Toshiba made a CMOS-version, the TMPZ84C00, which is believed[by whom?] (but not verified) to be the same design also used by Zilog for its own CMOS Z84C00. There were also Z80-chips made by GoldStar (now LG) and the BU18400 series of Z80-clones (including DMA, PIO, CTC, DART and SIO) in NMOS and CMOS made by ROHM Electronics.

In East Germany, an unlicensed clone of the Z80, known as the U880, was manufactured. It was very popular and was used in Robotron's and VEB Mikroelektronik Mühlhausen's computer systems (such as the KC85-series) and also in many self-made computer systems. In Romania another unlicensed clone could be found, named MMN80CPU and produced by Microelectronica, used in home computers like TIM-S, HC, COBRA.

Also, several clones of Z80 were created in the Soviet Union, notable ones being the T34BM1, also called КР1858ВМ1 (parallelling the Soviet 8080-clone KR580VM80A). The first marking was used in pre-production series, while the second had to be used for a larger production. Though, due to the collapse of Soviet microelectronics in the late 1980s, there are many more T34BM1s than КР1858ВМ1s.[citation needed]

-

Mostek Z80: MK3880

-

Toshiba Z84C00

-

Soviet T34BM1 Z80 clone

Derivatives

- Compatible with the original Z80

- Hitachi developed the HD64180, a microcoded and partially dynamic Z80 in CMOS, with on chip peripherals and a simple MMU giving a 1 MB address space. It was later second sourced by Zilog, initially as the Z64180, and then in the form of the slightly modified Z180[47] which has bus protocol and timings better adapted to Z80 peripheral chips. Z180 has been maintained and further developed under Zilog's name, the newest versions being based on the fully static S180/L180 core with very low power draw and EMI (noise).

- Toshiba developed the 84 pin Z84013 / Z84C13 and the 100 pin Z84015 / Z84C15 series of "intelligent peripheral controllers", basically ordinary NMOS and CMOS Z80 cores with Z80 peripherals, watch dog timer, power on reset, and wait state generator on the same chip. Manufactured by Sharp as well as Toshiba. These products are today second sourced by Zilog.[48]

- The 32-bit Z80 compatible Zilog Z380, introduced 1994, is used mainly in telecom equipment.[citation needed]

- Zilog's fully pipelined Z80 compatible eZ80[49] with an 8/16/24-bit word length and a linear 16 MB address space was introduced in 2001. It exists in versions with on chip SRAM or flash memory, as well as with integrated peripherals. One variant has on chip MAC (media access controller), and available software include a TCP/IP stack. In contrast with the Z800 and Z280, there are only a few added instructions (primarily LEAs, PEAs, and variable-address 16/24-bit loads), but instructions are instead executed between 2 and 11 times as clock cycle efficient as on the original Z80 (with a mean value around 3-5 times). It is currently specified for clock frequencies up to 50 MHz.

- Kawasaki developed the binary compatible KL5C8400 which is approximately 1.2-1.3 times as clock cycle efficient as the original Z80 and can be clocked at up to 33 MHz. Kawasaki also produces the KL5C80A1x family, which has peripherals as well as a small RAM on chip; it is approximately as clock cycle efficient as the eZ80 and can be clocked at up to 10 MHz (2006).[50]

- The NEC µPD9002 was a hybrid CPU compatible with both Z80 and x86 families.

- The Chinese Actions Semiconductor's audio processor family of chips (ATJ2085 and others) contains a Z80-compatible MCUs together with a 24-bit dedicated DSP processor.[51] These chips are used in many MP3 and media player products.

- The T80 (VHDL) and TV80 (Verilog) synthesizable soft cores are available from OpenCores.org.[52]

- Non-compatible

- The Toshiba TLCS 900 series of high volume (mostly OTP) microcontrollers are based on the Z80; they share the same basic BC,DE,HL,IX,IY register structure, and largely the same instructions, but are not binary compatible, while the previous TLCS 90 is Z80-compatible.[53]

- The NEC 78K series microcontrollers are based on the Z80; they share the same basic BC,DE,HL register structure, and has similar (but differently named) instructions; not binary compatible.

- Partly compatible

- Rabbit Semiconductor's Rabbit 2000/3000/4000 microprocessors/microcontrollers[54] are based on the HD64180/Z180 architecture, although they are not fully binary compatible.[55]

- No longer produced

- The ASCII Corporation R800 was a fast 16-bit processor used in MSX TurboR computers; it was software, but not hardware compatible with the Z80 (signal timing, pinout & function of pins differ from the Z80).

- Zilog's NMOS Z800 and CMOS Z280 were 16-bit Z80-implementations (before the HD64180 / Z180) with a 16 MB paged MMU address space; they added many orthogonalizations and addressing modes to the Z80 instruction set. Minicomputer features — such as user and system modes, multiprocessor support, on chip MMU, on chip instruction and data cache and so on — were seen rather as more complexity than as functionality and support for the (usually electronics-oriented) embedded systems designer, it also made it very hard to predict instruction execution times.[citation needed]

- Certain arcade games such as Pang/Buster Bros use an encrypted "Kabuki" Z80 CPU manufactured by VLSI Technology, where the decryption keys are stored in its internal battery-backed memory, to avoid piracy and illegal bootleg games.[56]

Notable uses

Desktop computers

During the late 1970s and early 1980s, the Z80 was used in a great number of fairly anonymous business-oriented machines with the CP/M operating system, a combination that dominated the market at the time.[57][58] Four well-known examples of Z80 business computers running CP/M are the Heathkit H89, the portable Osborne 1, the Kaypro series, and the Epson QX-10. Less well-known was the expensive high-end Otrona Attache.[59] Some systems used multi-tasking operating system software (like MP/M or Morrow's Micronix) to share the one processor between several concurrent users.

Multiple home computers were introduced that used the Z80 as the main processor or as a plug-in option to allow access to software written for the Z80.

In 1981, Multitech (later to become Acer) introduced the Microprofessor I, a simple and inexpensive training system for the Z80 microprocessor. Currently, it is still manufactured and sold by Flite Electronics International Limited in Southampton, England.

Portable and handheld computers

Use of the Z80 in lighter, battery-operated devices became more widespread with the availability of CMOS versions of the processor. It also inspired the development of other CMOS based processors, such as the LH5801[60] from Sharp. The Sharp PC-1500, a BASIC-programmable pocket computer was released in 1981, followed by the improved Sharp PC-1600 in 1986 and the Sharp PC-E220 in 1991. Laptops which could run the CP/M operating system just like the desktop machines followed with Epson PX-8 Geneva in 1984, and in 1985 the Epson PX-4 and Bondwell-2. While the laptop market in subsequent years moved to more powerful Intel 8086 processors and the MS-DOS operating system, light-weight Z80-based systems with a longer battery life were still being introduced, such as the Cambridge Z88 in 1988 and the Amstrad NC100 in 1992. The Z80-derived Z8S180 also found its way into an early pen-operated personal digital assistant, the Amstrad PenPad PDA600 in 1993. Hong Kong-based VTech produced a line of small laptop computers called 'Lasers' based on a Z80.[61][62] The last two were the Laser PC5[63] and PC6.[64]

Starting with the TI-81 in 1990, Texas Instruments has manufactured a long line of graphing calculators based on the Z80. The TI-84 Plus series, introduced in 2004, is still in production as of 2019. The TI-84 Plus CE series, introduced in 2015, uses the Z80-derived Zilog eZ80 processor and is also still in production as of 2019. TI also produced a line of pocket organizers (ended in 2000) using Toshiba processors built around a Z80 core; the first of these was the TI PS-6200[65] and after a lengthy production run of some dozen models culminated in their PocketMate series.[66] Later models of the Sharp Wizard series of personal organizers were Z80 based.

Embedded systems and consumer electronics

The Zilog Z80 has long been a popular microprocessor in embedded systems and microcontroller cores,[23] where it remains in widespread use today.[3][67] Applications of the Z80 include uses in consumer electronics, industrial products, and electronic musical instruments. For example, Z80 was used in the groundbreaking music synthesizer Prophet-5,[68] as well as in the first MIDI synthesizer Prophet 600.[69] Casio used the Z80A in its PV-1000 video game console. The Z80 was also used in the Sega Master System and Game Gear consoles. The Sega Genesis also contained a Zilog Z80 which controlled the system’s sound chips but also provided backwards compatibility with Sega Master System games.

In the late 1980s, a series of Soviet landline phones called "AON" featured the Z80; these phones expanded the featureset of the landline with caller ID, different ringtones based on the caller, speed dial and so forth.[70]

See also

- BDS C

- Zilog eZ80

- S-100 bus

- Small C

- Small Device C Compiler

- SymbOS

- Transistor count

- Z88DK

- Micro-Professor MPF-I - Z80 training system

Footnotes

- ^ Zilog included several "traps" in the layout of the chip to try to delay this copying. According to Faggin, an NEC engineer later told him it had cost them several months of work, before they were able to get their μPD780 to function.

- ^ These were named the Z80 CTC (counter/timer), Z80 DMA (direct memory access), Z80 DART (dual asynchronous receiver-transmitter), Z80 SIO (synchronous communication controller), and Z80 PIO (parallel input/output)

- ^ Zilog manufactured the Z80 as well as most of their other products for many years until they sold their manufacturing plants and become the "fabless" company they are today.

- ^ Although the 8080 had 16-bit addition and 16-bit increment and decrement instructions, it had no explicit 16-bit subtraction, and no overflow flag. The Z80 complemented this with the ADC HL,rr and SBC HL,rr instructions which sets the new overflow flag accordingly. (The 8080 compatible ADD HL,rr does not.)

- ^ Notably to simultaneously handle the 32-bit mantissas of two operands in the 40-bit floating point format used in the Sinclair home computers. They were also used in a similar fashion in some earlier but lesser known Z80 based computers, such as the Swedish ABC 80 and ABC 800.

- ^ As this refresh does not need to transfer any data, just output sequential row-addresses, it occupies less than 1.5 T-states. The dedicated M1-signal (machine cycle one) in the Z80 can be used to allow memory chips the same amount of access time for instruction fetches as for data access, i.e almost two full T-states out of the 4T fetch cycle (as well as out of the 3T data read cycle). The Z80 could use memory with the same range of access times as the 8080 (or the 8086) at the same clock frequency. This long M1-signal (relative to the clock) also meant that the Z80 could employ about 4-5 times the internal frequency of a 6800, 6502 or similar using the same type of memory.

- ^ Unlike the original nMOS version, which used dynamic latches and could not be stopped for more than a few thousand clock cycles.

- ^ The related 8086 family also inherited this register design.

- ^ This variable HL pointer was actually the only way to access memory (for data) in the Datapoint 2200, and hence also in the Intel 8008. No direct addresses could be used to access data.

- ^ It is not actually possible to encode this instruction on the Intel 8086 or later processors. See Intel reference manuals.

References

- ^ Only in CMOS, National made no NMOS version, according to Oral History with Federico Faggin

- ^ Source: Federico Faggin oral history.

- ^ a b c Balch, Mark (2003-06-18). "Digital Fundamentals". Complete Digital Design: A Comprehensive Guide to Digital Electronics and Computer System Architecture. Professional Engineering. New York, New York: McGraw-Hill Professional. p. 122. ISBN 0-07-140927-0.

- ^ a b The Seybold report on professional computing. Seybold Publications. 1983.

In the 8-bit world, the two most popular microcomputers are the Z80 and 6502 computer chips.

- ^ Anderson (1994), p. 51.

- ^ Anderson (1994), p. 57.

- ^ a b Brock, Gerald W. (2003). The second information revolution. Harvard University Press. ISBN 978-0-674-01178-6.

- ^ "History of the 8-bit: travelling far in a short time". InfoWorld. Vol. 4, no. 47. Palo Alto, CA: Popular Computing Inc. 1982-11-29. pp. 58–60. ISSN 0199-6649.

- ^ Shima, Masatoshi; Federico Faggin; Ralph Ungermann (1976-08-19). "Z-80 chip set heralds third microprocessor generation". Electronics. 49 (17). New York: 32–33 McGraw–Hill.

- ^ See Federico Faggin, oral history.

- ^ Mathur (1989). Introduction to Microprocessors. p. 111. ISBN 978-0-07-460222-5.

The register architecture of the Z80 is more innovative than that of the 8085

- ^ Ciarcia 1981, pp. 31, 32

- ^ a b Wai-Kai Chen (2002). The circuits and filters handbook. CRC Press. p. 1943. ISBN 978-0-8493-0912-0.

interrupt processing commences according to the interrupt method stipulated by the IM i, i=0, 1, or 2, instruction. If i=1, for direct method, the PC is loaded with 0038H. If i=0, for vectored method, the interrupting device has the opportunity to place the op-code for one byte . If i=2, for indirect vector method, the interrupting device must then place a byte. The Z80 then uses this byte where one of 128 interrupt vectors can be selected by the byte.

- ^ "Z80 Special Reset".

- ^ Adrian, Andre. "Z80, the 8-bit Number Cruncher".

- ^ Popular Computing. McGraw-Hill. 1983. p. 15.

- ^ Markoff, John (1982-10-18). "Zilog's speedy Z80 soups up 8-bit to 16-bit performance". InfoWorld. InfoWorld Media Group. p. 1. ISSN 0199-6649.

- ^ Electronic design. Hayden. 1988. p. 142.

In addition to supporting the entire Z80 instruction set, the Z180

- ^ Ganssle, Jack G. (1992). "The Z80 Lives!".

The designers picked an architecture compatible with the Z80, giving Z80 users a completely software compatible upgrade path. The 64180 processor runs every Z80 instruction exactly as a Z80 does

- ^ "Down to the silicon: how the Z80's registers are implemented".

- ^ Kilobaud. 1001001. 1977. p. 22.

- ^ Zaks, Rodnay (1982). Programming the Z80 (3rd ed.). SYBEX. p. 62. ISBN 978-0-89588-069-7.

- ^ a b c Steve Heath. (2003). Embedded systems design. Oxford: Newnes. p. 21. ISBN 978-0-7506-5546-0.

- ^ "Z80 Flag Affection". www.z80.info. Thomas Scherrer. Retrieved 2016-06-14.

- ^ Frank Durda IV. "8080/Z80 Instruction Set". Archived from the original on 2016-02-11. Retrieved 2009-07-22.

- ^ "8080A/ 8-Bit N-Channel Microprocessor". Intel Component Data Catalog 1978. Santa Clara, CA: Intel Corporation. 1978. pp. 11–17.

All mnemonics copyright Intel Corporation 1977

- ^ Jump (

JP) instructions, which load the program counter with a new instruction address, do not themselves access memory. Absolute and relative forms of the jump reflect this by omitting the round brackets from their operands. Register based jump instructions such as "JP (HL)" include round brackets in an apparent deviation from this convention."Z80 Relocating Macro Assembler User's Guide" (PDF). p. B–2. Archived from the original (PDF) on 2011-07-20. Retrieved 2009-06-04. - ^ Scanlon, Leo J. (1988). 8086/8088/80286 assembly language. Brady Books. p. 12. ISBN 978-0-13-246919-7.

[…] The 8086 is software-compatible with the 8080 at the assembly-language level. […]

- ^ Nelson, Ross P. (January 1989) [1988]. The 80386 Book: Assembly Language Programmer's Guide for the 80386. Microsoft Programming Series (1 ed.). Microsoft Press. p. 2. ISBN 978-1-55615-138-5.

[…] An Intel translator program could convert 8080 assembler programs into 8086 assembler programs […]

- ^ a b "Z80 CPU Introduction". Zilog. 1995.

It has a language of 252 root instructions and with the reserved 4 bytes as prefixes, accesses an additional 308 instructions.

- ^ Sanchez, Julio; Canton, Maria P. (2008). Software Solutions for Engineers And Scientists. Taylor & Francis. p. 65. ISBN 978-1-4200-4302-0.

The 8-bit microprocessors that preceded the 80x86 family (such as the Intel 8080, the Zilog Z80, and the Motorola) did not include multiplication.

- ^ "8080/Z80 Instruction Sets". Quick and Dirty 8080 Assembler. Frank Durda. Archived from the original on 2016-02-11. Retrieved 2016-07-25.

- ^ Froehlich, Robert A. (1984). The free software catalog and directory. Crown Publishers. p. 133. ISBN 978-0-517-55448-7.

Undocumented Z80 codes allow 8 bit operations with IX and IY registers.

- ^ a b Bot, Jacco J. T. "Z80 Undocumented Instructions". Home of the Z80 CPU.

If an opcode works with the registers HL, H or L then if that opcode is preceded by #DD (or #FD) it works on IX, IXH or IXL (or IY, IYH, IYL), with some exceptions. The exceptions are instructions like LD H,IXH and LD L,IYH.

- ^ Robin Nixon The Amstrad Notepad Advanced User Guide ,Robin Nixon, 1993 ISBN 1-85058-515-6, pages 219-223

- ^ Zilog (2005). Z80 Family CPU User Manual (PDF). Zilog. p. 11.

- ^ Ciarcia 1981, p. 65

- ^ Zaks, Rodnay (1989). Programming the Z80. Sybex. p. 200. ISBN 978-0-89588-069-7.

ADD A, n Add accumulator with immediate data n. MEMORY Timing: 2 M cycles; 7 T states.

- ^ Ciarcia 1981, p. 63

- ^ Ciarcia 1981, p. 77

- ^ Ciarcia 1981, p. 36

- ^ Ciarcia 1981, p. 58

- ^ "Z80 User Manual, Special Registers pg. 3". www.zilog.com. Zilog. Retrieved 2016-06-14.

- ^ "Z80 Family CPU Peripherals User Manual" (PDF). EEWORLD Datasheet. ZiLOG. 2001. Archived from the original (PDF) on 2014-05-02. Retrieved 2014-04-30.

- ^ Young, Sean (1998). "Z80 Undocumented Features (in software behaviour)".

The I/O instructions use the whole of the address bus, not just the lower 8 bits. So in fact, you can have 65536 I/O ports in a Z80 system (the Spectrum uses this). IN r,(C), OUT (C),r and all the I/O block instructions put the whole of BC on the address bus. IN A,(n) and OUT (n),A put A*256+n on the address bus.

- ^ "Overview of the SHARP MZ-series". SharpMZ.org. Archived from the original on 2008-03-27. Retrieved 2011-07-28.

Most MZ's use the 8bit CPU LH0080 / Z80 [...]

- ^ Ganssle, Jack G. (1992). "The Z80 Lives!".

The 64180 is a Hitachi-supplied Z80 core with numerous on-chip "extras". Zilog's version is the Z180, which is essentially the same part.

- ^ Ganssle, Jack G. (1992). "The Z80 Lives!".

Both Toshiba and Zilog sell the 84013 and 84015, which are Z80 cores with conventional Z80 peripherals integrated on-board.

- ^ "EZ80 ACCLAIM Product Family". Zilog.

- ^ Electronic Business Asia. Cahners Asia Limited. 1997. p. 5.

Kawasaki's KL5C80A12, KL5C80A16 and KL5C8400 are high speed 8-bit MCUs and CPU. Their CPU code, KC80 is compatible with Zilog's Z80 at binary level. KC80 executes instructions about four times faster than Z80 at the same clock rate

- ^ "Hardware specs". S1mp3.org. 2005.

- ^ "Projects :: OpenCores".

- ^ "Section 6 MOS MPU, MCU, and Peripherals Market Trends" (PDF). p. 16.

- ^ Axelson, Jan (2003). Embedded ethernet and internet complete. Lakeview research. p. 93. ISBN 978-1-931448-00-0.

Rabbit Semiconductor's Rabbit 3000 microprocessor, which is a much improved and enhanced derivative of ZiLOG, Inc.'s venerable Z80 microprocessor.

- ^ Hyder, Kamal; Perrin, Bob (2004). Embedded systems design using the Rabbit 3000 microprocessor. Newnes. p. 32. ISBN 978-0-7506-7872-8.

The Rabbit parts are based closely on the Zilog Z180 architecture, although they are not binary compatible with the Zilog parts.

- ^ Cruz, Eduardo (2014-11-23). "Arcade Hacker: Capcom Kabuki CPU - Intro".

- ^ Holtz, Herman (1985). Computer work stations. Chapman and Hall. p. 223. ISBN 978-0-412-00491-9.

and CP/M continued to dominate the 8-bit world of microcomputers.

- ^ Dvorak, John C. (1982-05-10). "After CP/M, object oriented operating systems may lead the field". InfoWorld. Vol. 4, no. 18. InfoWorld Media Group. p. 20. ISSN 0199-6649.

The idea of a generic operating system is still in its infancy. In many ways it begins with CP/M and the mishmash of early 8080 and Z80 computers.

- ^ "Otrona Attache". Steve's Old Computer Museum. Steven Stengel. Retrieved 2019-03-05.

- ^ "Sharp PC-1500 Technical Reference Manual" (PDF).

- ^ "Poor Man's Laptop". Google Books. Popular Mechanics, April 1991, page 120. April 1991. Retrieved 2018-04-11.

- ^ "Laser PC4". Old Computer Museum. Retrieved 2018-04-11.

- ^ "Laser PC5 from VTech". Larwe dot com. Retrieved 2018-04-11.

- ^ "Laser PC6". Perfect Solutions dot com. Perfect Solutions. Archived from the original on 2018-05-21. Retrieved 2018-04-11.

- ^ "Texas Instruments PS-6200". Datamath Calculator Museum. Joerg Woerner. Retrieved 2019-06-18.

- ^ "Texas Instruments PocketMate 100". Datamath Calculator Museum. Joerg Woerner. Retrieved 2019-06-18.

- ^ Ian R. Sinclair. (2000). Practical electronics handbook. Oxford, Angleterre: Newnes. p. 204. ISBN 978-0-7506-4585-0.

- ^ "Gordon Reid's Vintage Synths - the Sequential Circuits Prophet 5 and Prophet 10". www.gordonreid.co.uk.

- ^ "Prophet 600: A Classic Synthesizer Gets Processor Upgrade". 2014-03-19.

- ^ "Making a demo for an old phone — AONDEMO". habr.com.

Further reading

- Datasheets and manuals

- Z80 Datasheet (NMOS); Zilog; 10 pages; 1978.

- Z80 Data Book (NMOS); Zilog; 131 pages; 1978.

- Z80 Datasheet (NMOS and CMOS); Zilog; 36 pages; 2002. Errata

- Z80 User Manual (NMOS and CMOS); Zilog; 332 pages; 2016.

- Z80 Peripheral User Manual (NMOS and CMOS); Zilog; 330 pages; 2001.

- Hardware books

- Build Your Own Z80 Computer - Design Guidelines and Application Notes; 1st Ed; Steve Ciarcia; Byte Books; 332 pages; 1981; ISBN 978-0070109629. (archive)

- Z80 Microprocessor - Architecture, Interfacing, Programming, and Design; 1st Ed; Ramesh Gaonkar; Macmillan; 674 pages; 1988; ISBN 978-0675205405. (archive)

- Z80 Users Manual - Pin Definitions, Control Signals, Peripherals, and More; 1st Ed; Joseph Carr; Reston; 338 pages; 1980; ISBN 978-0835995177. (archive)

- Microprocessor Interfacing Techniques; 3rd Ed; Rodnay Zaks and Austin Lesea; Sybex; 466 pages; 1979; ISBN 978-0-89588-029-1. (archive)

- Software books

- Programming the Z80; 3rd Ed; Rodnay Zaks; Sybex; 630 pages; 1980; ISBN 978-0895880949. (archive)

- Z80 Assembly Language Programming; 1st Ed; Lance Leventhal; Osborne/McGraw-Hill; 642 pages; 1979; ISBN 978-0931988219. (archive)

- 8080/Z80 Assembly Language - Techniques for Improved Programming; 1st Ed; Alan Miller; John Wiley & Sons; 332 pages; 1981; ISBN 978-0471081241. (archive)

- Z80 and 8080 Assembly Language Programming; 1st Ed; Kathe Spracklen; Hayden; 180 pages; 1979; ISBN 978-0810451674. (archive)

- Practical Microcomputer Programming - The Z80 - including Source for Resident Assembler and Debug Monitor; 1st Ed; Walter Weller; Northern Technology; 501 pages; 1978; ISBN 978-0930594053. (archive)

- Z80 Assembly Language Subroutines; 1st Ed; Lance Leventhal and Winthrop Saville; Osborne/McGraw-Hill; 512 pages; 1983; ISBN 978-0931988912. (archive)

- Undocumented Z80 Documented; Sean Young; v0.91; 52 pages; 2005. (archive)

- Reference cards

- Reference Card for the Z80 Microprocessor; Shirley & Nanos; Nanos Systems; 16 pages; 1981. (archive)

- Z80 Microprocessor Instant Reference Card; James Lewis; Micro Logic; 2 pages; 1981. (archive)

External links

- Z80 unofficial support page

- Z80 compatible second source chips at CPU World

- How Z80 registers are implemented in silicon

- Simulators / Emulators

- Z80 software emulators

- Yet Another Z80 Emulator

- Z80 Bus Emulator for education purpose - includes NEC's TK-80 training kit, ZX-80 microcomputer, CP/M 2.2 emulator

- Boards

- Grant's 7-chip Z80 board and 8/9-chip CP/M on breadboard

- Z80 microprocessor training board

- Linker3000 6-chip Z80 board

- RC2014 modern Z80 DIY kit

- CPUville Z80 DIY kit

- ZX81+35 board - improved Sinclair ZX81

- FPGA

- NextZ80 Z80 CPU core - Verilog source code - OpenCores

- A-Z80 Z80 CPU core - Verilog source code - OpenCores

- T80 Z80 CPU core - VHDL source code - OpenCores