SPARC T3

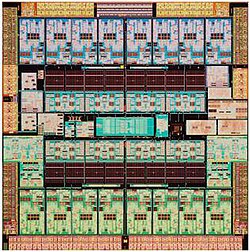

SPARC T3 micrograph | |

| General information | |

|---|---|

| Launched | 2010 |

| Marketed by | Oracle Corporation |

| Designed by | Sun Microsystems |

| Performance | |

| Max. CPU clock rate | 1.67 GHz |

| Architecture and classification | |

| Instruction set | SPARC V9 |

| Physical specifications | |

| Cores |

|

| Products, models, variants | |

| Core name |

|

| History | |

| Predecessor | UltraSPARC T2 |

| Successor | SPARC T4 |

The SPARC T3 microprocessor (previously known as UltraSPARC T3, codenamed Rainbow Falls, and also known as UltraSPARC KT or Niagara-3 during development) is a multithreading, multi-core CPU produced by Oracle Corporation (previously Sun Microsystems).[1][2][3] Officially launched on 20 September 2010, it is a member of the SPARC family, and the successor to the UltraSPARC T2.[4]

Performance

Overall single socket and multi-socket throughput increased with the T3 processor in systems, providing superior throughput with half the CPU socket requirements to its predecessor.

The throughput (SPEC CINT2006 rate) increased in single a socket T3-1 platform[5] in comparison to its predecessor T2+ processor in a dual-socket T5240 platform.[6]

Under simulated web serving workloads, dual-socket based SPARC T3 systems benchmarked better performance than quad-socket(previous generation) UltraSPARC T2+ systems (as well as competing dual and quad socket contemporary systems.)[7]

History

Online IT publication The Register incorrectly reported in June 2008 that the microprocessor would have 16 cores, each with 16 threads. In September 2009 they published a roadmap that instead showed 8 threads per core.[8] During the Hot Chips 21 conference Sun revealed the chip has a total of 16 cores and 128 threads.[9][10] According to the ISSCC 2010 presentation:

"A 16-core SPARC SoC processor enables up to 512 threads in a 4-way glueless system to maximize throughput. The 6MB L2 cache of 461GB/s and the 308-pin SerDes I/O of 2.4Tb/s support the required bandwidth. Six clock and four voltage domains, as well as power management and circuit techniques, optimize performance, power, variability and yield trade-offs across the 377mm2 die."[11]

Support for the UltraSPARC T3 was confirmed on July 16, 2010 when the ARCBot under Twitter noted unpublished PSARC/2010/274 which revealed a new "-xtarget value for UltraSPARC T3" being included in OpenSolaris.[12]

During Oracle OpenWorld in San Francisco on September 20, 2010, the processor was officially launched as the "SPARC T3" (dropping the "Ultra" prefix in its name), accompanied by new systems and new reported benchmarks claiming world-record performance.[3] Varied real-world application benchmarks were released with full system disclosures.[13][14][15] Internationally recognized SPEC benchmarks were also released with full system disclosures.[16][17] Oracle disclosed that SPARC T3 was built with a 40 nm process.[18]

Features

- 8 or 16 CPU cores

- 8 hardware threads per core

- 6 MB Level 2 cache

- 2 embedded coherency controllers

- 6 coherence links

- 14 unidirectional lanes per coherence link

- SMP to 4 sockets without glue circuitry

- 4 DDR3 SDRAM memory channels

- Embedded PCI Express I/O interfaces

- 16 Embedded Crypto Acceleration Engines

- Hardware random number generator

- 2 embedded 1GigE/10GigE interfaces

- 2.4 Tbit/s aggregate throughput per socket

Systems

With the release of the SPARC T3 chip, the new brand of Oracle SPARC T-series servers was introduced to the market, effectively replacing CMT (UltraSPARC T2/T2 Plus) machines from the previous SPARC Enterprise product line. Fewer physical products from the former server line were refreshed with the T3 chip, reducing the total number of servers respectively to four:[19]

- One Socket SPARC T3-1 2U Rack Server[20]

- One Socket SPARC T3-1B Blade Server[21]

- Two Socket SPARC T3-2 Server [22]

- Four Socket SPARC T3-4 Server [23]

Virtualization

Like the prior T1, T2, and T2+ processors, the T3 supports Hyper-Privileged execution mode. The T3 supports up to 128 Oracle VM Server for SPARC domains (a feature formerly known as Logical Domains).[23]

Performance improvement versus T2 and T2+

The SPARC T3 processor is effectively two T2+ processors on a single die.[24] The T3 has:

- Double the cores (16) of a T2 or T2+

- Double the 10Gig Ethernet ports (2) over a T2+

- Double the crypto accelerator cores (16) over a T2 or T2+

- Crypto engines support more algorithms than the T2 or T2+ including: DES, Triple DES, AES, RC4, SHA-1, SHA256/384/512, Kasumi, Galois Field, MD5, RSA to 2048 key, ECC, CRC32[18]

- Over 1.9x Cryptography Performance Throughput Increase[25]

- Faster DDR3 RAM interface over the T2 or T2+ DDR2 interface

- Double the throughput[20]

- Double the memory capacity[20]

- Quadruple the I/O throughput[20]

- Two PCIe 2.0 eight lane interfaces vs one PCIe former generation eight lane interface[24]

See also

- UltraSPARC T1 – The predecessor to T2, also Sun's first chip-multithreaded CPU

- SPARC T4

References

- ^ High-end server chips breaking records | Speeds and Feeds - CNET News

- ^ Sun, IBM push multicore boundaries

- ^ a b Oracle Unveils SPARC T3 Processor and SPARC T3 Systems

- ^ Oracle Unveils SPARC T3 Processor and SPARC T3 Systems

- ^ Oracle Corporation SPARC T3-1, 2008-03, retrieved 2011-07-19

- ^ Sun SPARC Enterprise T5240, 2008-03, retrieved 2010-11-25

- ^ SPECweb2005, 2008-03, retrieved 2011-07-19

- ^ http://www.theregister.co.uk/2009/09/11/sun_sparc_roadmap_revealed/

- ^ Sanjay Patel, Stephen Phillips and Allan Strong. "Sun's Next-Generation Multi-threaded Processor - Rainbow Falls: Sun's Next Generation CMT Processor". HOT CHIPS 21.

- ^ Stokes, Jon (February 9, 2010). "Two billion-transistor beasts: POWER7 and Niagara 3". Ars Technica.

- ^ J. Shin, K. Tam, D. Huang, B. Petrick, H. Pham, C. Hwang, H. Li, A. Smith, T. Johnson, F. Schumacher, D. Greenhill, A. Leon, A. Strong. "A 40nm 16-Core 128-Thread CMT SPARC SoC Processor". ISSCC 2010.

- ^ Twitter / ARCbot: PSARC/2010/274 New compiler

- ^ http://blogs.sun.com/BestPerf/entry/20100927_sparct3_1_obay_fusion

- ^ http://blogs.sun.com/BestPerf/entry/20100923_sparct3_1_peoplesoft_fms

- ^ http://blogs.sun.com/BestPerf/entry/20100922_sparct3_1_siebel_crm

- ^ http://blogs.sun.com/BestPerf/entry/sparc_t3_2_sets_world

- ^ http://blogs.sun.com/BestPerf/entry/sparc_t3_4_sets_world

- ^ a b http://www.oracle.com/us/products/servers-storage/servers/sparc-enterprise/t-series/sparc-t3-chip-ds-173097.pdf

- ^ SPARC Servers

- ^ a b c d SPARC T3-1 | Web Infrastructure Server | Oracle

- ^ T3-1B | Best Blade for Infrastructure Apps | Oracle

- ^ SPARC T3-2 | Web Infrastructure Server | Oracle

- ^ a b SPARC T3-4 | Consolidation and Virtualization | Oracle

- ^ a b http://www.c0t0d0s0.org/archives/6921-SPARC-T3-some-data.html

- ^ http://blogs.sun.com/BestPerf/entry/20100920_sparc_t3_pk11rsaperf