Direct Media Interface

This article needs additional citations for verification. (January 2014) |

| Direct Media Interface | |

| Created by | Intel |

|---|---|

| Supersedes | Intel Hub Architecture |

| Speed |

|

| Style | Serial |

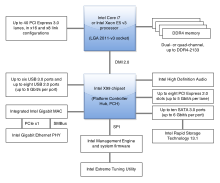

In computing, Direct Media Interface (DMI) is Intel's proprietary link between the northbridge (or CPU) and southbridge (e.g. Platform Controller Hub family) chipset on a computer motherboard.[1] It was first used between the 9xx chipsets and the ICH6, released in 2004.[2]: 1 Previous Intel chipsets had used the Intel Hub Architecture to perform the same function, and server chipsets use a similar interface called Enterprise Southbridge Interface (ESI).[3] While the "DMI" name dates back to ICH6, Intel mandates specific combinations of compatible devices, so the presence of a DMI does not guarantee by itself that a particular northbridge–southbridge combination is allowed.

DMI is essentially PCI Express, using multiple lanes and differential signaling to form a point-to-point link. Most implementations use a ×8 or ×4 link, while some mobile systems (e.g. 915GMS, 945GMS/GSE/GU and the Atom N450) use a ×2 link, halving the bandwidth. The original implementation provides 10 Gbit/s (1 GB/s) in each direction using a ×4 link. The DMI provides support for concurrent traffic and isochronous data transfer capabilities.[2]: 3 [4]

DMI replaced FSB (Front Side Bus) which was eliminated in 2009.[5]

Versions

[edit]DMI 1.0, introduced in 2004 with a data transfer rate of 1 GB/s with a ×4 link.

DMI 2.0, introduced in 2011, doubles the data transfer rate to 2 GB/s with a ×4 link. It is used to link an Intel CPU with the Intel Platform Controller Hub (PCH), which supersedes the historic implementation of a separate northbridge and southbridge.[6]: 14

DMI 3.0, released in August 2015, allows the 8 GT/s transfer rate per lane, for a total of four lanes and 3.93 GB/s for the CPU–PCH link. It is used by two-chip variants of the Intel Skylake microprocessors, which are used in conjunction with Intel 100 Series chipsets;[7][8] some low power (Skylake-U onwards) and ultra low power (Skylake-Y onwards) mobile Intel processors have the PCH integrated into the physical package as a separate die, referred to as OPI (On Package DMI interconnect Interface)[9] and effectively following the system on a chip (SoC) design layout.[10] On 9 March 2015, Intel announced the Broadwell-based Xeon D as its first enterprise platform to fully incorporate the PCH in an SoC configuration.[11]

In 2021, with the release of 500 series chipsets, Intel increased the amount of DMI 3.0 lanes from four to eight, doubling the bandwidth.[12]

DMI 4.0, released on November 4, 2021 with 600 series chipsets, doubles the bandwidth each lane provides and is two times faster when compared to DMI 3.0. The number of DMI 4.0 lanes depends on chipset model used.[13]

Implementations

[edit]2005 Centrino mobile platform.[2]: 3 At the time DMI linked the GMCH and I/O Controller Hub.[2]: 3

Northbridge devices supporting a northbridge DMI are the Intel 915-series, 925-series, 945-series, 955-series, 965-series, 975-series, G31/33, P35, X38, X48, P45 and X58.[citation needed]

Processors supporting a northbridge DMI and, therefore, not using a separate northbridge, are the Intel Atom, Intel Core i3, Intel Core i5, and Intel Core i7 (8xx, 7xx and 6xx, but not 9xx). Processors supporting a northbridge DMI 2.0 and, therefore not using a separate northbridge, are the 2000, 3000, 4000, and 5000 series of the Intel Core i3, Core i5 and Core i7.

Southbridge devices supporting a southbridge DMI are the ICH6, ICH7, ICH8, ICH9, ICH10, NM10, P55, H55, H57, Q57, PM55, HM55, HM57, QM57 and QS57.[citation needed]

PCH devices supporting DMI 2.0 are the Intel B65, H61, H67, P67, Q65, Q67, Z68, HM65, HM67, QM67, QS67, B75, H77, Q75, Q77, Z75, Z77, X79, HM75, HM76, HM77, QM77, QS77, UM77, H81, B85, Q85, Q87, H87, Z87, H97, Z97, C222, C224, C226, X99, H110,[14] and H310.[15]

PCH devices supporting DMI 3.0 are the Intel Z170, H170, HM170, Q170, QM170, Q150, B150, C236, CM236, C232, and C620.[16][17][18][19][20][21][22][23][24][25] The Intel 200 series, B360,[26] H370,[27] Q370,[28] Z370,[29] Z390,[30] C246,[31] and Intel 400 series chipsets also support DMI 3.0.

PCH devices supporting DMI 4.0 are the Intel 600 and 700 Series chipsets.[32][33]

See also

[edit]- Front-side bus – Type of computer communication interface

- List of interface bit rates

References

[edit]- ^ "What Is the Direct Media Interface (DMI) of Intel Processors?". Intel. Retrieved 2023-06-05.

- ^ a b c d "Second-Generation Intel Centrino TM Mobile Technology" (PDF). Intel Technology Journal. 9 (1). February 17, 2005. doi:10.1535/itj.0901. ISSN 1535-864X.

- ^ "Intel 5520 Chipset and Intel 5500 Chipset Datasheet" (PDF). Intel. March 2009. Retrieved 2014-11-06.

- ^ "Direct Media Interface (DMI) - 1.0 - ID:721073 | Intel NUC 12 Extreme / Pro X". edc.intel.com. Retrieved 2023-06-05.

- ^ "Core i7 975 review (Page 4)". 2 June 2009.

- ^ "Desktop 3rd Generation Intel Core Processor Family, Desktop Intel Pentium Processor Family, and Desktop Intel Celeron Processor Family: Datasheet - Volume 1 of 2" (PDF). External Design Specification (EDS). Intel. November 2013. Retrieved 2014-01-28.

- ^ Ian Cutress (2015-08-05). "The Skylake CPU Architecture – The Intel 6th Gen Skylake Review: Core i7-6700K and i5-6600K Tested". AnandTech. Retrieved 2015-08-06.

- ^ Ian Cutress (2015-08-05). "Intel Skylake Z170 Motherboards: A Quick Look at 55+ New Products". AnandTech. Retrieved 2015-08-06.

- ^ Ganesh T S (2016-05-09). "Choosing the Right SSD for a Skylake-U System". AnandTech. Retrieved 2016-11-16.

- ^ Gennadiy Shvets (2014-06-26). "More details on Skylake processors". cpu-world.com. Retrieved 2014-07-01.

- ^ Cutress, Ian (9 March 2015). "Intel Xeon D Launched: 14nm Broadwell SoC for Enterprise". AnandTech. Retrieved 18 June 2015.

- ^ "Intel Rocket Lake (14nm) Review: Core i9-11900K, Core i7-11700K, and Core i5-11600K".

- ^ "Intel 600 Series chipsets". Intel Ark. Retrieved 3 April 2022.

- ^ "Intel H110 Chipset (Intel GL82H110 PCH)". Intel ARK (Product Specs). Retrieved 28 January 2016.

- ^ "Intel H310 Chipset Product Specifications". Intel ARK (Product Specs). Retrieved 2018-07-22.

- ^ "Intel Z170 Chipset (Intel GL82Z170 PCH)". Intel ARK (Product Specs). Retrieved 28 January 2016.

- ^ "Intel H170 Chipset (Intel GL82H170 PCH)". Intel ARK (Product Specs). Retrieved 28 January 2016.

- ^ "Mobile Intel HM170 Chipset (Intel GL82HM170 PCH)". Intel ARK (Product Specs). Retrieved 28 January 2016.

- ^ "Intel Q170 Chipset (Intel GL82Q170 PCH)". Intel ARK (Product Specs). Retrieved 28 January 2016.

- ^ "Mobile Intel QM170 Chipset (Intel GL82QM170 PCH)". Intel ARK (Product Specs). Retrieved 28 January 2016.

- ^ "Intel Q150 Chipset (Intel GL82Q150 PCH)". Intel ARK (Product Specs). Retrieved 28 January 2016.

- ^ "Intel B150 Chipset (Intel GL82B150 PCH)". Intel ARK (Product Specs). Retrieved 28 January 2016.

- ^ "Intel C236 Chipset (Intel GL82C236 PCH)". Intel ARK (Product Specs). Retrieved 28 January 2016.

- ^ "Mobile Intel CM236 Chipset (Intel GL82CM236 PCH)". Intel ARK (Product Specs). Retrieved 28 January 2016.

- ^ "Intel C232 Chipset (Intel GL82C232 PCH)". Intel ARK (Product Specs). Retrieved 28 January 2016.

- ^ "Intel B360 Chipset Product Specifications". Intel ARK (Product Specs). Retrieved 2018-07-22.

- ^ "Intel H370 Chipset Product Specifications". Intel ARK (Product Specs). Retrieved 2018-07-22.

- ^ "Intel Q370 Chipset Product Specifications". Intel ARK (Product Specs). Retrieved 2018-07-22.

- ^ "Intel Z370 Chipset Product Specifications". Intel ARK (Product Specs). Retrieved 2018-07-22.

- ^ "Intel Z390 Chipset Product Specifications". Intel ARK (Product Specs). Retrieved 2018-07-22.

- ^ "Intel C246 Chipset Product Specifications". Intel ARK (Product Specs). Retrieved 2018-07-22.

- ^ "Intel 600 Series chipsets". Intel Ark. Retrieved 3 April 2022.

- ^ "Intel 700 Series Chipsets". Intel Ark. Retrieved 11 October 2022.