CUDA

Compute Unified Device Architecture (CUDA) is a parallel computing architecture developed by Nvidia for graphics processing.[1] CUDA is the computing engine in Nvidia graphics processing units (GPUs) that is accessible to software developers through variants of industry standard programming languages. Programmers use 'C for CUDA' (C with Nvidia extensions and certain restrictions), compiled through a PathScale Open64 C compiler,[2] to code algorithms for execution on the GPU. CUDA architecture shares a range of computational interfaces with two competitors: the Khronos Group's OpenCL[3] and Microsoft's DirectCompute.[4] Third party wrappers are also available for Python, Perl, Fortran, Java, Ruby, Lua, Haskell, MATLAB, IDL, and native support in Mathematica. CUDA programming in the web browser is freely available for individual non-commercial purposes in NCLab.

CUDA gives developers access to the virtual instruction set and memory of the parallel computational elements in CUDA GPUs. Using CUDA, the latest Nvidia GPUs become accessible for computation like CPUs. Unlike CPUs however, GPUs have a parallel throughput architecture that emphasizes executing many concurrent threads slowly, rather than executing a single thread very quickly. This approach of solving general purpose problems on GPUs is known as GPGPU.

In the computer game industry, in addition to graphics rendering, GPUs are used in game physics calculations (physical effects like debris, smoke, fire, fluids); examples include PhysX and Bullet. CUDA has also been used to accelerate non-graphical applications in computational biology, cryptography and other fields by an order of magnitude or more.[5][6][7][8] An example of this is the BOINC distributed computing client.[9]

CUDA provides both a low level API and a higher level API. The initial CUDA SDK was made public on 15 February 2007, for Microsoft Windows and Linux. Mac OS X support was later added in version 2.0,[10] which supersedes the beta released February 14, 2008.[11] CUDA works with all Nvidia GPUs from the G8x series onwards, including GeForce, Quadro and the Tesla line. CUDA is compatible with most standard operating systems. Nvidia states that programs developed for the G8x series will also work without modification on all future Nvidia video cards, due to binary compatibility.

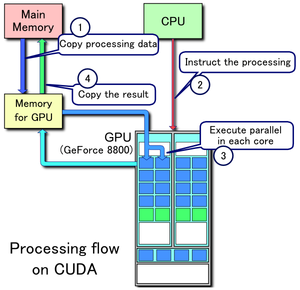

1. Copy data from main mem to GPU mem

2. CPU instructs the process to GPU

3. GPU execute parallel in each core

4. Copy the result from GPU mem to main mem

Background

The GPU, as a specialized processor, addresses the demands of real-time high-resolution 3D graphics compute-intensive tasks. As of 2012[update] GPUs have evolved into highly parallel multi core systems allowing very efficient manipulation of large blocks of data. This design is more effective than general-purpose CPUs for algorithms where processing of large blocks of data is done in parallel, such as:

- push-relabel maximum flow algorithm

- fast sort algorithms of large lists

- two-dimensional fast wavelet transform

For instance, the parallel nature of molecular dynamics simulations is suitable for CUDA implementation.[citation needed]

Advantages

CUDA has several advantages over traditional general-purpose computation on GPUs (GPGPU) using graphics APIs:

- Scattered reads – code can read from arbitrary addresses in memory

- Shared memory – CUDA exposes a fast shared memory region (up to 48KB per Multi-Processor) that can be shared amongst threads. This can be used as a user-managed cache, enabling higher bandwidth than is possible using texture lookups.[12]

- Faster downloads and readbacks to and from the GPU

- Full support for integer and bitwise operations, including integer texture lookups

Limitations

- Texture rendering is not supported (CUDA 3.2 and up addresses this by introducing "surface writes" to cuda Arrays, the underlying opaque data structure).

- Copying between host and device memory may incur a performance hit due to system bus bandwidth and latency (this can be partly alleviated with asynchronous memory transfers, handled by the GPU's DMA engine)

- Threads should be running in groups of at least 32 for best performance, with total number of threads numbering in the thousands. Branches in the program code do not impact performance significantly, provided that each of 32 threads takes the same execution path; the SIMD execution model becomes a significant limitation for any inherently divergent task (e.g. traversing a space partitioning data structure during ray tracing).

- Unlike OpenCL, CUDA-enabled GPUs are only available from Nvidia[13]

- Valid C/C++ may sometimes be flagged and prevent compilation due to optimization techniques the compiler is required to employ to use limited resources.

- CUDA (with compute capability 1.x) uses a recursion-free, function-pointer-free subset of the C language, plus some simple extensions. However, a single process must run spread across multiple disjoint memory spaces, unlike other C language runtime environments.

- CUDA (with compute capability 2.x) allows a subset of C++ class functionality, for example member functions may not be virtual (this restriction will be removed in some future release). [See CUDA C Programming Guide 3.1 - Appendix D.6]

- Double precision (CUDA compute capability 1.3 and above)[14] deviate from the IEEE 754 standard: round-to-nearest-even is the only supported rounding mode for reciprocal, division, and square root. In single precision, denormals and signalling NaNs are not supported; only two IEEE rounding modes are supported (chop and round-to-nearest even), and those are specified on a per-instruction basis rather than in a control word; and the precision of division/square root is slightly lower than single precision.

Supported GPUs

Compute capability table (version of CUDA supported) by GPU and card. Also available directly from Nvidia

| Compute capability (version) |

GPUs | Cards |

|---|---|---|

| 1.0 | G80, G92, G92b, G94, G94b | GeForce 8800GTX/Ultra, 9400GT, 9600GT, 9800GT, Tesla C/D/S870, FX4/5600, 360M, GT 420 |

| 1.1 | G86, G84, G98, G96, G96b, G94, G94b, G92, G92b | GeForce 8400GS/GT, 8600GT/GTS, 8800GT/GTS, 9600 GSO, 9800GTX/GX2, GTS 250, GT 120/30/40, FX 4/570, 3/580, 17/18/3700, 4700x2, 1xxM, 32/370M, 3/5/770M, 16/17/27/28/36/37/3800M, NVS420/50 |

| 1.2 | GT218, GT216, GT215 | GeForce 210, GT 220/40, FX380 LP, 1800M, 370/380M, NVS 2/3100M |

| 1.3 | GT200, GT200b | GeForce GTX 260, GTX 275, GTX 280, GTX 285, GTX 295, Tesla C/M1060, S1070, Quadro CX, FX 3/4/5800 |

| 2.0 | GF100, GF110 | GeForce (GF100) GTX 465, GTX 470, GTX 480, Tesla C2050, C2070, S/M2050/70, Quadro Plex 7000, GeForce (GF110) GTX570, GTX580, GTX590 |

| 2.1 | GF104, GF114, GF116, GF108, GF106 | GeForce GT 430, GT 440, GTS 450, GTX 460, GTX 550 Ti, GTX 560, GTX 560 Ti, 500M, Quadro 600, 2000, 4000, 5000, 6000 |

| 3.0 | GK104, GK106, GK107 | GeForce GTX 690, GTX 680, GTX 670, GeForce GTX 660M, GeForce GT 650M, GeForce GT 640M |

A table of devices officially supporting CUDA (Note that many applications require at least 256 MB of dedicated VRAM, and some recommend at least 96 cuda cores).[13]

see full list here: http://developer.nvidia.com/cuda-gpus

|

|

|

Version features and specifications

| Feature support (unlisted features are supported for all compute capabilities) |

Compute capability (version) | |||||

|---|---|---|---|---|---|---|

| 1.0 | 1.1 | 1.2 | 1.3 | 2.x | 3.0 | |

| Integer atomic functions operating on 32-bit words in global memory |

No | Yes | ||||

| atomicExch() operating on 32-bit floating point values in global memory | ||||||

| Integer atomic functions operating on 32-bit words in shared memory |

No | Yes | ||||

| atomicExch() operating on 32-bit floating point values in shared memory | ||||||

| Integer atomic functions operating on 64-bit words in global memory | ||||||

| Warp vote functions | ||||||

| Double-precision floating-point operations | No | Yes | ||||

| Atomic functions operating on 64-bit integer values in shared memory |

No | Yes | ||||

| Floating-point atomic addition operating on 32-bit words in global and shared memory | ||||||

| _ballot() | ||||||

| _threadfence_system() | ||||||

| _syncthreads_count(), _syncthreads_and(), _syncthreads_or() | ||||||

| Surface functions | ||||||

| 3D grid of thread block | ||||||

| Technical specifications | Compute capability (version) | |||||

|---|---|---|---|---|---|---|

| 1.0 | 1.1 | 1.2 | 1.3 | 2.x | 3.0 | |

| Maximum dimensionality of grid of thread blocks | 2 | 3 | ||||

| Maximum x-, y-, or z-dimension of a grid of thread blocks | 65535 | 231-1 | ||||

| Maximum dimensionality of thread block | 3 | |||||

| Maximum x- or y-dimension of a block | 512 | 1024 | ||||

| Maximum z-dimension of a block | 64 | |||||

| Maximum number of threads per block | 512 | 1024 | ||||

| Warp size | 32 | |||||

| Maximum number of resident blocks per multiprocessor | 8 | 16 | ||||

| Maximum number of resident warps per multiprocessor | 24 | 32 | 48 | 64 | ||

| Maximum number of resident threads per multiprocessor | 768 | 1024 | 1536 | 2048 | ||

| Number of 32-bit registers per multiprocessor | 8 K | 16 K | 32 K | 64 K | ||

| Maximum amount of shared memory per multiprocessor | 16 KB | 48 KB | ||||

| Number of shared memory banks | 16 | 32 | ||||

| Amount of local memory per thread | 16 KB | 512 KB | ||||

| Constant memory size | 64 KB | |||||

| Cache working set per multiprocessor for constant memory | 8 KB | |||||

| Cache working set per multiprocessor for texture memory | Device dependent, between 6 KB and 8 KB | |||||

| Maximum width for 1D texture reference bound to a CUDA array |

8192 | 65536 | ||||

| Maximum width for 1D texture reference bound to linear memory |

227 | |||||

| Maximum width and number of layers for a 1D layered texture reference |

8192 x 512 | 16384 x 2048 | ||||

| Maximum width and height for 2D texture reference bound to a CUDA array |

65536 x 32768 | 65536 x 65535 | ||||

| Maximum width and height for 2D texture reference bound to a linear memory |

65000 x 65000 | 65000 x 65000 | ||||

| Maximum width and height for 2D texture reference bound to a CUDA array supporting texture gather |

N/A | 16384 x 16384 | ||||

| Maximum width, height, and number of layers for a 2D layered texture reference |

8192 x 8192 x 512 | 16384 x 16384 x 2048 | ||||

| Maximum width, height and depth for a 3D texture reference bound to linear memory or a CUDA array |

2048 x 2048 x 2048 | 4096 x 4096 x 4096 | ||||

| Maximum width (and height) for a cubemap texture reference | N/A | 16384 | ||||

| Maximum width (and height) and number of layers for a cubemap layered texture reference | N/A | 16384 x 2046 | ||||

| Maximum number of textures that can be bound to a kernel |

128 | 256 | ||||

| Maximum width for a 1D surface reference bound to a CUDA array |

Not supported |

65536 | ||||

| Maximum width and height for a 2D surface reference bound to a CUDA array |

65536 x 32768 | |||||

| Maximum number of surfaces that can be bound to a kernel |

8 | 16 | ||||

| Maximum number of instructions per kernel |

2 million | 512 million | ||||

| Architecture specifications | Compute capability (version) | ||||||

|---|---|---|---|---|---|---|---|

| 1.0 | 1.1 | 1.2 | 1.3 | 2.0 | 2.1 | 3.0 | |

| Number of cores for integer and floating-point arithmetic functions operations | 8[15] | 32 | 48 | 192 | |||

| Number of special function units for single-precision floating-point transcendental functions | 2 | 4 | 8 | 32 | |||

| Number of texture filtering units for every texture address unit or render output unit (ROP) | 2 | 4 | 8 | 32 | |||

| Number of warp schedulers | 1 | 2 | 2 | 4 | |||

| Number of instructions issued at once by scheduler | 1 | 1 | 2[16] | 2 | |||

For more information please visit this site: http://www.geeks3d.com/20100606/gpu-computing-nvidia-cuda-compute-capability-comparative-table/ and also read Nvidia CUDA programming guide.[17]

Example

This example code in C++ loads a texture from an image into an array on the GPU:

texture<float, 2, cudaReadModeElementType> tex;

void foo()

{

cudaArray* cu_array;

// Allocate array

cudaChannelFormatDesc description = cudaCreateChannelDesc<float>();

cudaMallocArray(&cu_array, &description, width, height);

// Copy image data to array

cudaMemcpyToArray(cu_array, image, width*height*sizeof(float), cudaMemcpyHostToDevice);

// Set texture parameters (default)

tex.addressMode[0] = cudaAddressModeClamp;

tex.addressMode[1] = cudaAddressModeClamp;

tex.filterMode = cudaFilterModePoint;

tex.normalized = false; // do not normalize coordinates

// Bind the array to the texture

cudaBindTextureToArray(tex, cu_array);

// Run kernel

dim3 blockDim(16, 16, 1);

dim3 gridDim((width + blockDim.x - 1)/ blockDim.x, (height + blockDim.y - 1) / blockDim.y, 1);

kernel<<< gridDim, blockDim, 0 >>>(d_data, height, width);

// Unbind the array from the texture

cudaUnbindTexture(tex);

} //end foo()

__global__ void kernel(float* odata, int height, int width)

{

unsigned int x = blockIdx.x*blockDim.x + threadIdx.x;

unsigned int y = blockIdx.y*blockDim.y + threadIdx.y;

if (x < width && y < height) {

float c = tex2D(tex, x, y);

odata[y*width+x] = c;

}

}

Below is an example given in Python that computes the product of two arrays on the GPU. The unofficial Python language bindings can be obtained from PyCUDA.[18]

import pycuda.compiler as comp

import pycuda.driver as drv

import numpy

import pycuda.autoinit

mod = comp.SourceModule("""

__global__ void multiply_them(float *dest, float *a, float *b)

{

const int i = threadIdx.x;

dest[i] = a[i] * b[i];

}

""")

multiply_them = mod.get_function("multiply_them")

a = numpy.random.randn(400).astype(numpy.float32)

b = numpy.random.randn(400).astype(numpy.float32)

dest = numpy.zeros_like(a)

multiply_them(

drv.Out(dest), drv.In(a), drv.In(b),

block=(400,1,1))

print dest-a*b

Additional Python bindings to simplify matrix multiplication operations can be found in the program pycublas.[19]

import numpy

from pycublas import CUBLASMatrix

A = CUBLASMatrix( numpy.mat([[1,2,3],[4,5,6]],numpy.float32) )

B = CUBLASMatrix( numpy.mat([[2,3],[4,5],[6,7]],numpy.float32) )

C = A*B

print C.np_mat()

Language bindings

- Fortran - FORTRAN CUDA, PGI CUDA Fortran Compiler

- Haskell - Data.Array.Accelerate

- IDL - GPULib

- Java - jCUDA, JCuda, JCublas, JCufft

- Lua - KappaCUDA

- Mathematica - CUDALink

- MATLAB - Parallel Computing Toolbox, Distributed Computing Server,[20] and 3rd party packages like Jacket.

- .NET - CUDA.NET; CUDAfy.NET .NET kernel and host code, CURAND, CUBLAS, CUFFT

- Perl - KappaCUDA, CUDA::Minimal

- Python - PyCUDA, KappaCUDA

- Ruby - KappaCUDA

Current CUDA architectures

The current generation CUDA architecture (codename: Fermi) which is standard on Nvidia's released (GeForce 400 Series [GF100] (GPU) 2010-03-27)[21] GPU is designed from the ground up to natively support more programming languages such as C++. It has eight times the peak double-precision floating-point performance compared to Nvidia's prior-generation Tesla GPU. It also introduced several new features[22] including:

- up to 1024 CUDA cores and 6.0 billion transistors on the GTX 590

- Nvidia Parallel DataCache technology

- Nvidia GigaThread engine

- ECC memory support

- Native support for Visual Studio

Current and future usages of CUDA architecture

- Accelerated rendering of 3D graphics

- Accelerated interconversion of video file formats

- Accelerated encryption, decryption and compression

- Distributed Calculations, such as predicting the native conformation of proteins

- Medical analysis simulations, for example virtual reality based on CT and MRI scan images.

- Physical simulations, in particular in fluid dynamics.

- Real Time Cloth Simulation OptiTex.com - Real Time Cloth Simulation

- The Search for Extra-Terrestrial Intelligence (SETI@Home) program[23][24]

See also

- GeForce 8 series

- GeForce 9 series

- GeForce 200 Series

- GeForce 400 Series

- GeForce 500 Series

- GeForce 600 Series

- Nvidia Quadro - Nvidia's workstation graphics solution

- Nvidia Tesla - Nvidia's first dedicated general purpose GPU (graphics processing unit)

- GPGPU - general purpose computation on GPUs

- OpenCL - The cross-platform standard supported by both NVidia and AMD/ATI

- DirectCompute - Microsoft API for GPU Computing in Windows Vista and Windows 7

- BrookGPU

- Vectorization (parallel computing)

- Lib Sh

- Nvidia Corporation

- Graphics processing unit (GPU)

- Stream processing

- Shader

- Larrabee

- Molecular modeling on GPU

- rCUDA - An API for computing on remote computers

References

- ^ Nvidia CUDA Programming Guide Version 1.0

- ^ Nvidia Clears Water Muddied by Larrabee Shane McGlaun (Blog) - August 5, 2008 - DailyTech

- ^ First OpenCL demo on a GPU on YouTube

- ^ DirectCompute Ocean Demo Running on Nvidia CUDA-enabled GPU on YouTube

- ^ Giorgos Vasiliadis, Spiros Antonatos, Michalis Polychronakis, Evangelos P. Markatos and Sotiris Ioannidis (2008, Boston, MA, USA). "Gnort: High Performance Network Intrusion Detection Using Graphics Processors" (PDF). Proceedings of the 11th International Symposium on Recent Advances in Intrusion Detection (RAID).

{{cite journal}}: Check date values in:|year=(help); Unknown parameter|month=ignored (help)CS1 maint: multiple names: authors list (link) CS1 maint: year (link) - ^ Schatz, M.C., Trapnell, C., Delcher, A.L., Varshney, A. (2007). "High-throughput sequence alignment using Graphics Processing Units". BMC Bioinformatics. 8:474: 474. doi:10.1186/1471-2105-8-474. PMC 2222658. PMID 18070356.

{{cite journal}}: CS1 maint: multiple names: authors list (link) CS1 maint: unflagged free DOI (link) - ^ Pyrit - Google Code http://code.google.com/p/pyrit/

- ^ Use your Nvidia GPU for scientific computing, BOINC official site (December 18, 2008)

- ^ Nvidia CUDA Software Development Kit (CUDA SDK) - Release Notes Version 2.0 for MAC OSX

- ^ CUDA 1.1 - Now on Mac OS X- (Posted on Feb 14, 2008)

- ^ Silberstein, Mark (2007). "Efficient computation of Sum-products on GPUs" (PDF).

- ^ a b "CUDA-Enabled Products". CUDA Zone. Nvidia Corporation. Retrieved 2008-11-03.

- ^ CUDA and double precision floating point numbers

- ^ Cores perform only single-precision floating-point arithmetics. There is 1 double-precision floating-point unit.

- ^ The first scheduler is in charge of the warps with an odd ID and the second scheduler is in charge of the warps with an even ID.

- ^ Template:PDFlink, Page 136 of 160 (Version 4.2 April 5, 2012)

- ^ PyCUDA

- ^ pycublas

- ^ "MATLAB Adds GPGPU Support". 2010-09-20.

- ^ http://www.hardware.info/nl-NL/video/wmGTacRpaA/nVidia_GeForce_GTX_480_special/ Hardware.info broadcast about Nvidia GeForce GTX 470 and 480

- ^ http://www.nvidia.com/object/fermi_architecture.html The Current Generation CUDA Architecture, Code Named Fermi

- ^ http://setiathome.berkeley.edu/cuda.php

- ^ http://setiathome.berkeley.edu/cuda_faq.php